(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6254674号 (P6254674)

(45) 発行日 平成29年12月27日(2017.12.27)

(24) 登録日 平成29年12月8日 (2017.12.8)

(51) Int.Cl. F 1

GO9F 9/33 (2006.01) GO9F 9/33 GO9F 9/302 (2006.01) GO9F 9/302 C HO1L 33/00 (2010.01) HO1L 33/00 L

請求項の数 17 (全 35 頁)

最終頁に続く

(21) 出願番号 特願2016-500743 (P2016-500743)

(86) (22) 出願日 平成26年3月6日 (2014.3.6)

(65) 公表番号 特表2016-512347 (P2016-512347A)

(43) 公表日 平成28年4月25日 (2016. 4. 25)

(86) 国際出願番号PCT/US2014/021259(87) 国際公開番号W02014/149864

(87) 国際公開日 平成26年9月25日 (2014.9.25) 審査請求日 平成27年11月13日 (2015.11.13)

(31) 優先権主張番号 13/842,879

(32) 優先日 平成25年3月15日 (2013.3.15)

(33) 優先権主張国 米国 (US)

(31) 優先権主張番号 13/842, 925 (32) 優先日 平成25年3月15日 (2013. 3. 15)

(33) 優先権主張国 米国 (US)

(73)特許権者 503260918

アップル インコーポレイテッド

アメリカ合衆国 95014 カリフォルニア州 クパチーノ インフィニット ル

ープ 1

(74)代理人 100094569

弁理士 田中 伸一郎

(74)代理人 100088694

弁理士 弟子丸 健

(74)代理人 100067013

弁理士 大塚 文昭

(74)代理人 100086771

弁理士 西島 孝喜

(54) 【発明の名称】 冗長性スキームを備えた発光ダイオードディスプレイパネル

## (57)【特許請求の範囲】

## 【請求項1】

前置審查

冗長性スキームを備えたディスプレイパネルであって、

サブ画素のアレイを含む画素エリアを含むディスプレイ基板と、

前記サブ画素のアレイ内の冗長マイクロLEDデバイスのペアのアレイであって、各サブ画素は冗長マイクロLEDデバイスのペアを含み、対応するサブ画素内の各冗長マイクロLEDデバイスのペアは同じ原色発光で発光するように設計され、各冗長マイクロLEDデバイスが、無機半導体系材料からなるp-nダイオード含む、冗長マイクロLEDデバイスのペアのアレイと、

前記冗長マイクロLEDデバイスのペアのアレイに電気的に接触した1つ以上の上部電極層と、

を備え、

<u>前記</u>冗長マイクロLEDデバイスのペアのアレイは1つ以上の欠落したマイクロLEDデバイスを含み、

前記サブ画素のアレイは、第1のサブ画素のアレイと、第2のサブ画素のアレイと、第3のサブ画素のアレイと、を含み、前記第1、第2、及び第3のサブ画素のアレイは、異なる原色発光で発光するように設計されたことを特徴とする、冗長性スキームを備えたディスプレイパネル。

## 【請求項2】

前記第1のサブ画素のアレイは、赤色原色発光で発光するように設計され、前記第2の

サブ画素のアレイは緑色原色発光で発光するように設計され、前記第3のアレイサブ画素 アレイは、青色原色発光で発光するように設計されたことを特徴とする、請求項1に記載 の冗長性スキームを備えたディスプレイパネル。

## 【請求項3】

各マイクロ L E D デバイスは、最大幅 1 ~ 1 0 0 μ m であることを特徴とする、請求項 1 に記載の冗長性スキームを備えたディスプレイパネル。

#### 【請求項4】

各マイクロLEDデバイスは、最大幅 1 ~ 3 0  $\mu$  m であることを特徴とする、請求項 3 に記載の冗長性スキームを備えたディスプレイパネル。

#### 【請求項5】

各マイクロLEDデバイスは、pドープ層、nドープ層、及び前記pドープ層と前記nドープ層との間の量子井戸層を含むことを特徴とする、請求項4に記載の冗長性スキームを備えたディスプレイパネル。

## 【請求項6】

前記サブ画素のアレイを切替及び駆動するための回路を更に備えることを特徴とする、 請求項1に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項7】

前記各マイクロLEDデバイスが前記ディスプレイ基板上の対応する別個の接合層に分散された上部導電性コンタクト、下部導電性コンタクト、及び下部接合層と、を有し、かつ前記1つ以上の上部電極層は前記冗長マイクロLEDデバイスのペアのアレイの前記上部導電性コンタクトと電気的に接している、請求項6に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項8】

前記1つ以上の欠落したマイクロLEDデバイスを覆うパッシベーション層材料を含み、該パッシベーション層材料が前記冗長性マイクロLEDデバイスのペアの前記上部導電性コンタクトを覆っていないことを特徴とする、請求項7に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項9】

前記1つ以上の上部電極層を、前記サブ画素のアレイ間を走る接地タイラインから電気的に切断するために、前記1つ以上の欠落したマイクロLEDデバイスを超えて前記1つ以上の上部電極層内に1つ以上の切れ目を更に備えることを特徴とする、請求項7に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項10】

各サブ画素は、第1のランディングエリアと第2のランディングエリアとを含み、対応する冗長マイクロLEDデバイスのペアの第1のマイクロLEDデバイスは前記第1のランディングエリアに接合され、対応する冗長マイクロLEDデバイスのペアの第2のマイクロLEDデバイスは前記第2のランディングエリアに接合されることを特徴とする、請求項7に記載の冗長性スキームを備えたディスプレイパネル。

## 【請求項11】

少なくとも1つの前記サブ画素のための前記第1のランディングエリアは、欠落したマイクロLEDデバイスを含み、かつ前記回路から電気的に切断されることを特徴とする、 請求項10に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項12】

前記少なくとも1つの前記サブ画素のための前記第1のランディングエリアは、前記回路から前記第1のランディングエリアを電気的に切断するためにカットされることを特徴とする、請求項11に記載の冗長性スキームを備えたディスプレイパネル。

#### 【請求項13】

前記回路は、前記冗長マイクロLEDデバイスのペアのアレイと並んで前記画素エリア内の前記ディスプレイ基板に接合された、マイクロコントローラチップのアレイ内に包含されることを特徴とする、請求項10に記載の冗長性スキームを備えたディスプレイパネ

10

20

30

40

ル。

## 【請求項14】

各マイクロコントローラチップは、スキャン駆動回路及びデータ駆動回路に接続されることを特徴とする、請求項13に記載の冗長性スキームを備えたディスプレイパネル。

## 【請求項15】

前記回路は前記ディスプレイ基板内に包含されることを特徴とする、請求項<u>10</u>に記載の冗長性スキームを備えたディスプレイパネル。

### 【請求項16】

前記1つ以上の上部電極層は、前記冗長マイクロLEDデバイスのペアのアレイに電気的に接触する単一の上部電極層であることを特徴とする、請求項1に記載の冗長性スキームを備えたディスプレイパネル。

【請求項17】

前記単一の上部電極層は、平坦化層に形成された複数の開口を通してサブ画素のアレイ間を走る複数の接地タイラインに電気的に接触することを特徴とする、請求項<u>16</u>に記載の冗長性スキームを備えたディスプレイパネル。

【発明の詳細な説明】

【背景技術】

[0001]

(分野)

[0002]

本発明の実施形態は、ディスプレイシステムに関する。より詳しくは、本発明の実施形態は、マイクロ発光ダイオードを組み込んだディスプレイシステムに関する。

(背景技術)

[0003]

フラットパネル型ディスプレイは、幅広い電子機器において普及している。一般的なフラットパネル型ディスプレイは、アクティブマトリクス型ディスプレイ及びパッシブマトリクス型ディスプレイを含む。アクティブマトリクス型ディスプレイパネルにおける各画素は、アクティブ駆動回路により駆動される一方、パッシブマトリクス型ディスプレイパネルにおける各画素は、かかる駆動回路を使用しない。最新のコンピュータディスプレイ、スマートフォン、及びテレビ等、高解像度カラーディスプレイパネルは、典型的に、より優れた画質のためにアクティブマトリクス型ディスプレイパネル構造を用いる。

[0004]

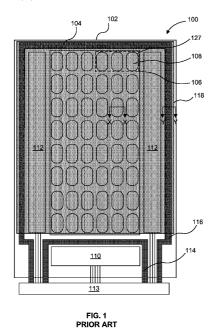

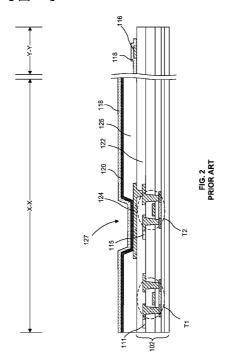

商業用途におけるディスプレイパネルの一種として、アクティブマトリクス型有機発光 ダイオード(AMOLED)ディスプレイパネルがある。図1は、トップエミッション型 AMOLEDディスプレイパネルの上面視の図である。図2は、図1の画素エリア104 内のX-X線及び、基板102上の画素エリア104外のいかなるエリアである非画素エ リア内の接地リング116を横切るY-Y線による、側断面視の図である。図1及び図2 に示すAMOLEDディスプレイパネル100は、一般に、画素エリア104と画素エリ ア102の外にある非画素エリアとを支持する、薄膜トランジスタ(TFT)基板102 を含む。TFT基板102は、バックプレーンとも呼ばれる。画素エリア及び非画素エリ アを付加的に含むように更に処理されたTFT基板は、バックプレーンと呼ばれることも よくある。AMOLEDで用いられる2つの主要なTFT基板技術は、多結晶シリコン( poly-Si)及びアモルファスシリコン(a-Si)を含む。これらの技術は、フレ キシブルAMOLEDディスプレイを製造するためのフレキシブルプラスチック基板上に 低温度(200 未満)で直接アクティブマトリクスバックプレーンを製造する可能性を 提供する。画素エリア104は、一般に、マトリクス状に配置された画素106及びサブ 画素108並びにサブ画素を駆動及び切り替えるために各サブ画素に接続されたTFT及 びキャパシタのセットを含む。非画素エリアは、一般に、データ信号(Vdata)をサ ブ画素に送信可能にするために各サブ画素のデータラインに接続されるデータ駆動回路1 10、スキャン信号(Vscan)をサブ画素に送信可能にするためにサブ画素のスキャ

20

10

30

40

ンラインに接続されるスキャン駆動回路112、電源信号(Vdd)をTFTに送信するための電源供給ライン114、及び接地信号(Vss)をサブ画素のアレイに送信するための接地リング116を含む。示されるように、データ駆動回路、スキャン駆動回路、電源供給ライン、及び接地リングはすべて、フレキシブル回路基板(FCB)113に接続されており、フレキシブル回路基板は電源供給ライン114に電力を供給するための電源、及び接地リング116に電気的に接続された電源接地ラインを含む。

#### [0005]

例示的なAMOLEDバックプレーン構成において、有機薄膜120及び上部電極118が画素エリア104内のあらゆるサブ画素108の上部に配置される。有機薄膜120は、正孔注入層、正孔輸送層、発光層、電子輸送層、及び電子注入層等、複数層を含んでよい。有機薄膜120の複数層は、典型的に、画素エリア104上全体にわたって形成されるが、発光層は多くの場合、シャドウマスクの補助により、サブ画素開口127内及びサブ画素108のアレイの発光エリアに対応する下部電極層124上にのみ配置される。次に上部電極層118は、接地信号をサブ画素のアレイに送信するために、上部電極118層が接地リング116に重なるように、画素エリア104内及び非画素エリア内の有機薄膜の上部に配置される。このように、サブ画素108はそれぞれ対応する下層のTFT回路で個別に処理され得る一方、均一な接地信号が画素エリア104の上部に供給される

### [0006]

例示される特定の実装において、TFT基板102は、データ駆動回路110からのデータライン111に接続されるスイッチングトランジスタT1、及び電源供給ライン114に接続される電力ライン115に接続される駆動トランジスタT2を含む。スイッチングトランジスタT1のゲートはまた、スキャン駆動回路112からのスキャンライン(図示せず)に接続され得る。平坦化層122はTFT基板の上部に形成され、開口がTFT作業回路を露出させるように形成される。例示されるように、下部電極層124は、TFT回路と電気的に接続されるように平坦化層上に形成される。電極層の形成に続いて、画素定義層125が、サブ画素108のアレイの発光エリアに対応するサブ画素開口127のアレイを含んで形成され、それに続き、パターン化された画素定義層の上部に及びパターン化された画素定義層125のサブ画素開口127カに、有機層120及び上部電極層118が成膜される。上部電極層118は、追加的に、非画素エリア内に接地リング116に電気的に接続して形成される。

## [0007]

平坦化層122は、段差により有機層120及び下部電極層124が短絡するのを防ぐ(又は保護する)よう機能し得る。例示的な平坦化層122の材料は、ベンゾシクロブテン(BCB)及びアクリルを含む。画素定義層125は、ポリイミドなどの材料により形成され得る。下部電極124は、一般に、インジウムスズ酸化物(ITO)、ITO/Ag、ITO/Ag/ITO、ITO/Ag/インジウム亜鉛酸化物(IZO)、又はITO/Ag合金/ITO上に形成される。上部電極層118は、トップエミッション用ITO等の透明材料で形成される。

### [00008]

AMOLEDディスプレイパネルは、通常、液晶ディスプレイ(LCD)パネルより少ない電力を消費するが、AMOLEDディスプレイパネルは依然として、バッテリ駆動デバイスにおいて電力を消費する主要なものである。バッテリの寿命を延ばすために、ディスプレイパネルの電力消費量を減らすことが必要である。

#### 【発明の概要】

## [0009]

冗長性スキームを備えたディスプレイパネル及び製造の方法を記述する。一実施形態において、ディスプレイパネルは、画素エリア及び非画素エリアを備えたディスプレイ基板を含む。画素エリアは、サブ画素のアレイ、及びサブ画素のアレイ内の対応する下部電極のアレイを含む。マイクロLEDデバイスのペアのアレイは、下部電極のアレイに接合さ

10

20

30

40

れ、1つ以上の上部電極はマイクロLEDデバイスのペアのアレイに電気的に接触して形成される。マイクロLEDデバイスは、半導体材料で形成されてもよく、最大幅1~100µmであってよい。

## [0010]

ある用途例においては、ディスプレイ基板はTFT基板であってもよい。接地ラインは、TFT基板の非画素エリアに形成されてもよく、上部電極層のうち1つ以上は、接地ラインに電気的に接続されてもよい。一実施形態において、第1から電極層までは、マイクロLEDデバイスのペアの第1のマイクロLEDデバイスを接地ラインに電気的に接続し、別個の第2の上部電極層は、マイクロLEDデバイスのペアの第2のマイクロLEDデバイスを接地ラインに電気的に接続する。

#### [0011]

ある用途例においては、マイクロコントローラチップのアレイは、ディスプレイ基板に接合され、各下部電極は、マイクロコントローラチップに電気的に接続される。各マイクロコントローラチップは、スキャン駆動回路及びデータ駆動回路に接続され得る。接地ラインは、ディスプレイ基板の非画素エリア内に走ってもよく、上部電極層のうち1つ以上は、接地ラインに電気的に接続されてもよい。一実施形態において、第1の上部電極層は、マイクロLEDデバイスのペアの第1のマイクロLEDデバイスを接地ラインに電気的に接続し、別個の第2の上部電極層は、マイクロLEDデバイスのペアの第2のマイクロLEDデバイスを接地ラインに電気的に接続する。

## [0012]

一実施形態において、複数のマイクロLEDデバイスの不規則部分は、マイクロLEDデバイスのペアのアレイ内にある。例えば、不規則部分は、欠落したマイクロLEDデバイス、欠陥のあるマイクロLEDデバイス、及び汚損されたマイクロLEDデバイスであり得る。パッシベーション層材は、複数の不規則部分を保護するために使用し、複数の不規則部分を電気的に絶縁するために使用されてもよい。パッシベーション層材はまた、マイクロLEDデバイスのペアのアレイの側壁(例えば、量子井戸構造を含む)を保護するのに使用されてもよい。一実施形態においては、1つ以上の上部電極層が複数の不規則部分の直接上部に形成された場合であっても、1つ以上の上部電極層は、複数の不規則部分と電気的に接触しない。1つ以上の上部電極層はまた、他のどこかに形成されてもよく、又は複数の不規則部分の直接上部に形成されないように、複数の不規則部分の周りに形成されてもよい。一実施形態において、修復マイクロLEDデバイスは、マイクロLEDデバイスの不規則部分の1つを含む下部電極の1つに接合される。

#### [0013]

一実施形態では、ディスプレイパネルを形成する方法は、マイクロLEDデバイスのアレイにおける不規則部分を検出するための統合検査を含む。マイクロLEDデバイスのアレイは、1つ以上のキャリア基板からディスプレイ基板上の対応するサブ画素のアレイ内の対応する下部電極のアレイまで、静電転写され得る。そして、ディスプレイ基板の表面は、マイクロLEDデバイスのアレイにおける不規則部分を検出するために撮像され、次にパッシベーション層材は複数の不規則部分を電気的に絶縁するために、検出された複数の不規則部分の上部に形成される。そして、1つ以上の上部電極層は、複数の不規則部分と電気的に接触せずに、マイクロLEDデバイスのアレイに電気的に接触して形成されにつかの実施形態では、パッシベーション層材は、インクジェット印刷又はスクリーン印刷により形成され、1つ以上の上部電極層はインクジェット印刷又はスクリーン印刷により形成される。一実施形態では、1つ以上の上部電極層は、別個の上部電極層である。別の実施形態では、別個の上部電極層のうちの1つは、電気経路を接地ラインまでカットオフするようにスクライブされる。

#### [0014]

ディスプレイ基板の表面の撮像は、カメラにより行われる。一実施形態では、カメラから製造された画像は、欠落したマイクロLEDデバイス又は汚損されたマイクロLEDデバイス等の不規則部分を検出するために使用される。一実施形態では、撮像は、マイクロ

10

20

30

40

LEDデバイスのアレイに蛍光発光させるために、光源によりディスプレイ基板の表面を照らすことと、カメラによりマイクロLEDデバイスのアレイの蛍光を撮像することを含む。カメラが蛍光を撮像することにより製造された画像は、欠陥のあるマイクロLEDデバイスを検出するのに使用され得る。

### [0015]

一実施形態では、複数の修復マイクロLEDデバイスは、パッシベーション層材を複数の不規則部分の上部に形成する前に、複数の不規則部分に隣接した(例えば、同じ下部電極上に)ディスプレイ基板に転写され得る。この後、複数の不規則部分に電気的に接触せずに、マイクロLEDデバイスのアレイ及び複数の修復マイクロLEDデバイスに電気的に接触するように1つ以上の上部電極層を形成することが続き得る。

### [0016]

一実施形態では、冗長性スキームを備えたディスプレイパネルを形成する方法は、マイクロLEDデバイスのペアのアレイを1つ以上のキャリア基板からディスプレイ基板上の対応するサブ画素のアレイ内の対応する下部電極のアレイまで、静電転写することを含む。ディスプレイ基板の表面は、その後、マイクロLEDデバイスのペアのアレイ内の不規則部分を検出するために撮像される。パッシベーション層材は、次に、複数の不規則部分を電気的に絶縁するために、検出された複数の不規則部分の上部に形成されてもよい。1つ以上の上部電極層は、次に、マイクロLEDデバイスのペアのアレイに電気的に接触して形成される。

## [0017]

静電転写のある方法は、マイクロLEDデバイスの第1のアレイを第1のキャリア基板の第1のエリアからディスプレイ基板に静電転写し、マイクロLEDデバイスの第2のアレイを第1のキャリア基板の第2のエリアからディスプレイ基板に静電転写することを含む。例えば、第1及び第2のエリアは、一実施形態では、相関する欠陥が同じサブ画素に転写される可能性を減じるために、重なり合わない。静電転写の別の方法は、マイクロLEDデバイスの第1及び第2のアレイを異なるキャリア基板から静電転写することを含む。本発明の実施形態によると、静電転写は、別個の静電転写へッドを備えた各マイクロLEDデバイスを静電転写することを含み得る。

### [0018]

一実施形態では、ディスプレイ表面の表面を撮像することは、カメラで撮像することを含む。例えば、ラインスキャンカメラを使用してもよい。一実施形態では、カメラから製造された画像は、欠落したマイクロLEDデバイス又は汚損されたマイクロLEDデバイス等の、マイクロLEDデバイスのペアのアレイ内の不規則部分を検出するために使用される。一実施形態では、ディスプレイ基板の表面を撮像することは、マイクロLEDデバイスのアレイに蛍光発光させるために、光源によりディスプレイ基板の表面を照らすことと、欠陥のあるマイクロLEDデバイスを検出するためカメラによりマイクロLEDデバイスのアレイの蛍光を撮像することを更に含む。

### [0019]

一実施形態では、単一の上部電極層は、不規則部分を含む、マイクロLEDデバイスのペアのアレイの上部に形成される。パッシベーション層材は、上部電極層が不規則部分と電気的に接触しないように、不規則部分を覆ってもよい。

#### [0020]

一実施形態において、複数の別個の上部電極層は、マイクロLEDデバイスのペアのアレイの上部に形成される。パッシベーション層材は、不規則部分の直接上部に形成される時に、不規則部分を上部接触層から電気的に絶縁するために使用され得る。上部接触層はまた、不規則部分の直接上部に位置しないように、不規則部分の周囲に形成されてもよい。インクジェット印刷及びスクリーン印刷は、上部電極層だけでなくパッシベーション層材もまた形成するために適した成膜法であり得る。一実施形態では、複数の修復マイクロLEDデバイスは、パッシベーション層材を複数の不規則部分の上部に形成する前に、複数の不規則部分に隣接したディスプレイ基板に転写される。上部電極層はまた、修復マイ

10

20

30

40

クロLEDデバイス上及びそれに電気的に接触して形成され得る。

【図面の簡単な説明】

[0021]

- 【図1】トップエミッション型AMOLEDディスプレイパネルの上面視の図である。

- 【 図 2 】図 1 のトップエミッション型 A M O L E D ディスプレイパネルのX-X線及びY - Y線による、側面視の図である。

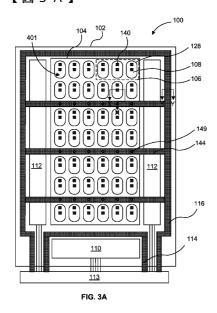

- 【図3A】本発明の一実施形態に係るアクティブマトリクス型ディスプレイパネルの上面 視の図である。

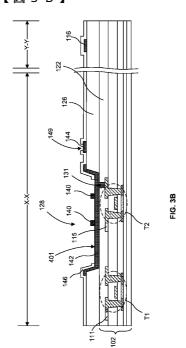

- 【図3B】本発明の一実施形態に係る、図3Aのアクティブマトリクス型ディスプレイパ ネルのX-X線及びY-Y線による、側面視の図である。

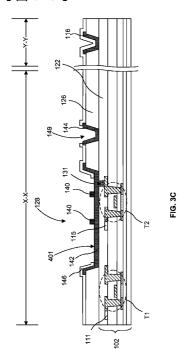

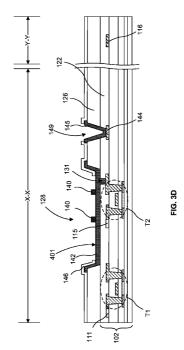

- 【図3C】本発明の一実施形態に係る、接地タイライン及び接地リングがパターン化され たバンク層内に形成された、図3Aのアクティブマトリクス型ディスプレイパネルのX-X線及びY-Y線による、側面視の図である。

- 【図3D】本発明の一実施形態に係る、接地タイライン及び接地リングがパターン化され たバンク層下に形成された、図3Aのアクティブマトリクス型ディスプレイパネルのX-X線及びY-Y線による、側面視の図である。

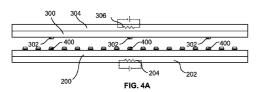

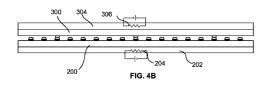

- 【図4A】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

- 【図4B】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

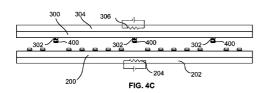

- 【図4C】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

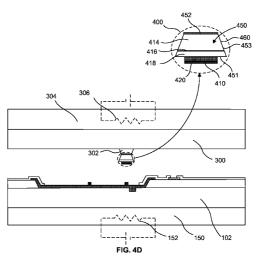

- 【図4D】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

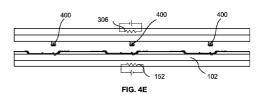

- 【図4E】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

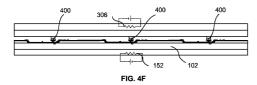

- 【図4F】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

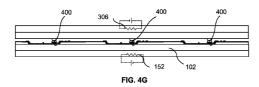

- 【図4G】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

- 【図4H】本発明の一実施形態に係る、TFT基板にマイクロLEDデバイスのアレイを 転写する方法のための側断面視の図である。

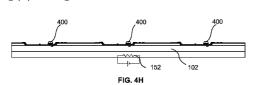

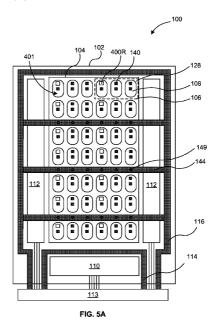

- 【図5A】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

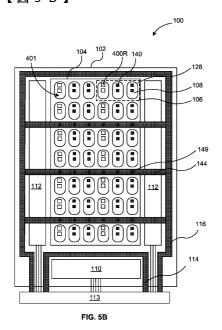

- 【図5B】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

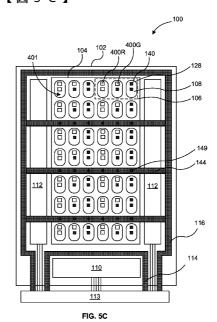

- 【図5C】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

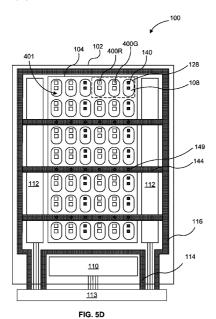

- 【図5D】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

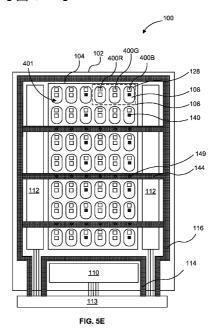

- 【図5日】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

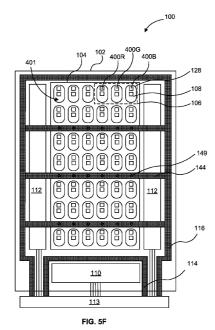

- 【図5F】本発明の一実施形態に係る、異なる色で発光するマイクロLEDデバイスのア レイを転写する一連ための上面視の図である。

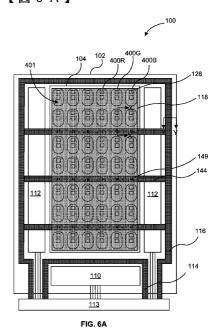

- 【図6A】一実施形態に係る、上部電極層の形成後のアクティブマトリクス型ディスプレ イパネルの上面視の図である。

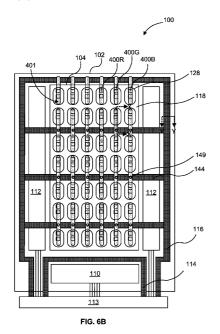

- 【図6B】一実施形態に係る、別個の上部電極層の形成後のアクティブマトリクス型ディ スプレイパネルの上面視の図である。

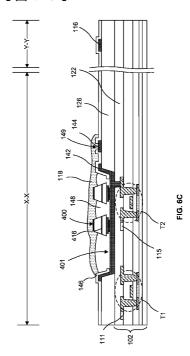

- 【図6C】本発明の一実施形態に係る、図6A又は図6Bのいずれかのアクティブマトリ クス型ディスプレイパネルのX-X線及びY-Y線による、側面視の図である。

10

20

30

40

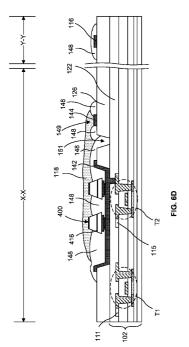

【図6D】本発明の一実施形態に係る、図6A又は図6Bのいずれかのアクティブマトリクス型ディスプレイパネルのX-X線及びY-Y線による、側面視の図である。

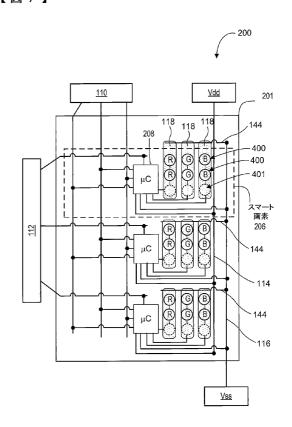

【図7】本発明の一実施形態に係る冗長性及び修復部位構成を含むスマート画素ディスプレイの上面視の概略図である。

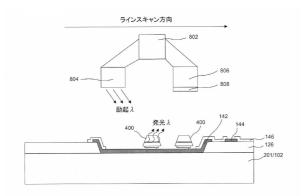

【図8A】本発明の一実施形態に係る、光源及びカメラを含む検査装置の側面視の概略図である。

【図8B】本発明の一実施形態に係る、スキャンパターンの上面視の概略図である。

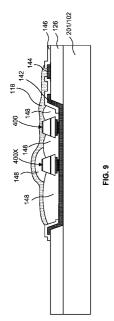

【図9】本発明の一実施形態に係る、欠陥のあるマイクロLEDデバイスを検出後に形成され得る例示的な構造の側断面視の図である。

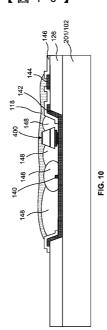

【図10】本発明の一実施形態に係る、欠落したマイクロLEDデバイスを検出後に形成され得る例示的な構造の側断面視の図である。

【図11】本発明の一実施形態に係る、欠陥のあるマイクロ L E D デバイスを検出後に形成され得る例示的な構造の側断面視の図である。

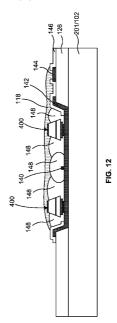

【図12】本発明の一実施形態に係る、欠落したマイクロLEDデバイスを検出後に形成され得る例示的な構造の側断面視の図である。

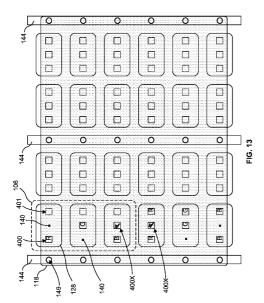

【図13】本発明の一実施形態に係る、様々な構成を含むマイクロLEDデバイスのアレイの上部に形成された上部電極層の上面視の概略図である。

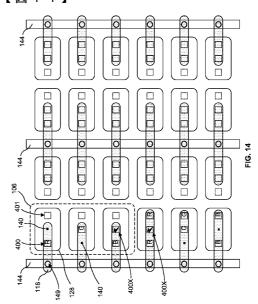

【図14】本発明の一実施形態に係る、様々な構成を含むマイクロLEDデバイスのアレイの上部に形成された複数の別個の上部電極層の上面視の概略図である。

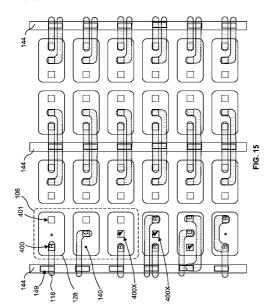

【図15】本発明の一実施形態に係る、様々な構成を含むマイクロLEDデバイスのアレイの上部に形成された複数の別個の上部電極層の上面視の概略図である。

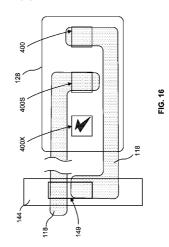

【図16】本発明の一実施形態に係る、スクライブされた上部電極層の上面視の概略図である。

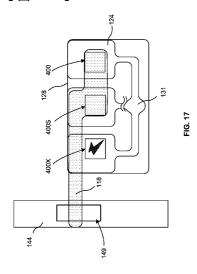

【図17】本発明の一実施形態に係る、スクライブされた下部電極層の上面視の概略図である

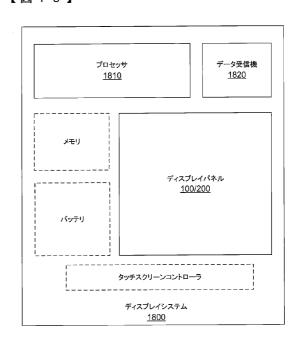

【図18】本発明の一実施形態に係る、ディスプレイシステムの概略図である。

【発明を実施するための形態】

[0022]

本発明の実施形態は、ディスプレイシステムに関する。より詳しくは、本発明の実施形態は発光ダイオードの冗長性スキームを備えたディスプレイに関する。

[0023]

ある態様において、本発明の実施形態は、ウェハベースの発光マイクロLEDデバイス を含む、アクティブマトリクス型ディスプレイパネルについて記述する。マイクロLED デバイスは、AMOLEDバックプレーンを形成するのに使用される薄膜エレクトロニク スの高歩留まりで低価格の混合材料により、ウェハベースのLEDデバイスの性能、効率 、信頼性を組み合わせる。本明細書内で使用される「マイクロ」デバイス又は「マイクロ 」LED構造という言葉は、本発明の実施形態に係る特定のデバイス又は構造体の記述的 大きさを指す場合がある。本明細書内で使用される時、「マイクロ」デバイス又は構造体 という言葉は、1~100μmの尺度を指すことが意図されている。しかし、本発明の実 施形態は必ずしもこれに限定されず、これら実施形態の特定の態様はより大きな尺度、又 は場合によってはより小さな尺度に適用できる場合があることを理解すべきである。一実 施形態において、ディスプレイパネルは、マイクロLEDデバイスが各サブ画素内のOL EDディスプレイパネルの有機層を交換した、典型的なOLEDディスプレイパネルに類 似する。本発明のいくつかの実施形態で利用され得る例示的なマイクロLEDデバイスが 米国特許出願番号13/372,222、米国特許出願番号13/436,260、米国 特許出願番号13/458,932、米国特許出願番号13/711,554、及び米国 特許出願番号13/749,647に記載され、これらはすべて本明細書に参照とするこ とによって組み込まれる。マイクロLEDデバイスは、発光において高効率であり、対角 線が10インチのLCD又はOLEDディスプレイの場合5~10ワットであるのに比べ 、非常に少ない電力(例えば、対角線が10インチのディスプレイの場合、250mW)

10

20

30

40

を消費し、それによりディスプレイパネルの電力消費量を減少させることができる。

## [0024]

他の態様において、本発明の実施形態は、複数の接合部位が、複数のマイクロLEDデバイスを例えば、サブ画素の各バンク開口内において、各下部電極上に接合させるのに利用可能である、冗長性スキームについて記述している。一実施形態において、冗長性スキームはとの接合層(例えば、インジム社)を含み、各接合層は、別個のマイクロLEDデバイスを受容するように設計される。一実施形態において、冗長性スキームはまた、マイクロLEDデバイスを受容するのに、分な大きさのバンク開口内の修復接合部位を含み得る。修復接合部位はまた、任意的的光色に対応することがあり、その発光色の複数のマイクロLEDデバイスを受容する。接合のマイクロLEDデバイスを受容する。接合ののうちの1つに接合されたマイクロLEDデバイスのうちの1つに欠陥がある場合のマイクロLEDデバイスが、欠陥のあるマイクロLEDデバイスを補う。また、修復接ののマイクロLEDデバイスが、欠陥のあるマイクロLEDデバイスを補う。また、修復接合部位は、所望により、追加のマイクロLEDデバイスに接合するのに使用され得る。このように、冗長性及び修復構成は、従来のAMOLEDディスプレイにすでに組み込まれた基本TFTアーキテクチャを変更する必要なく、ディスプレイパネル全体で均一な発光を改善可能なバックプレーン構造に統合される。

#### [0025]

他の側面において、本発明の実施形態は、マイクロLEDデバイスをキャリア基板からディスプレイ基板へ転写した後、欠陥のある、欠落した、又は汚損されたマイクロLEDデバイスを検出するための統合検査方法について記述する。このように、欠陥のある、欠落した、又は汚損されたマイクロLEDデバイスの検出は、代替のマイクロLEDデバイスを必要であれば潜在的に転写したり、マイクロLEDデバイス及び下部電極のパッシベーションに関わる後続の処理を変更したり、又は上部電極層の形成に関わる後続の処理を変更したりするために使用され得る。更に、統合検査方法は、検査のためにマイクロLEDデバイスに上部電気的コンタクトを備える必要がないように、製造プロセスに実装され得、検査は別個の電気的検査なしに実行され得る。

#### [0026]

種々の実施形態において、図を参照して説明がなされている。しかし、特定の実施形態は、これらの具体的な詳細のうちの1つ以上を伴わずに、又はその他の既知の方法及び構成との組み合わせで実施することができる。以下の説明において、本発明の完全な理解を提供するために、具体的な構成、寸法、及び工程などの数多くの具体的な詳細が明らかにされる。他の例では、本発明を不必要にあいまいにしないために、半導体の周知の工程及び製造技術について特に詳細な説明を行っていない。本明細書を通じた「一実施形態」への言及は、本実施形態と関連して述べる特定の機能、構造体、構成、又は特徴が、本発明に関する少なくとも一実施形態の中に含まれることを意味する。したがって、本明細書全体を通じて各所にある「一実施形態において」との記述は、必ずしも本発明の同一の実施形態を指すものではない。更に、特定の機構、構造体、構成、又は特性は、1つ以上の実施形態の中で任意の好適な方法で組み合わせることができる。

#### [0027]

本明細書で使用される用語「広がる」、「の上方に」、「への」、「間の」、及び「上に」は、他の層に対するある層の相対位置について言及する場合がある。ある層が別の層に「広がる」、「の上方に」若しくは「上に」あること、又は別の層「へと」若しくは「接触して」接合することは、別の層と直接接触する、又は1つ以上の介在層を有することが想定される。層と層「との間」の1つの層は、両方の層と直接接触している場合もあれば、1つ以上の介在層を有する場合もある。

#### [0028]

以下の記述がアクティブマトリクス型ディスプレイパネルに関して具体的になされることを理解すべきである。しかし、本実施形態は、これに限定されるものではない。特に、 冗長性スキーム、修復部位、及び欠陥のある、欠落した、又は汚損されたマイクロLED 10

20

30

40

20

30

40

50

デバイスを検出するための検査方法はまたパッシブマトリクス型ディスプレイパネル、並びに、照明の目的のための基板にも実装され得る。

## [0029]

次に図3A~図3Bを参照すると、AMOLEDバックプレーンと同様のバックプレー ンが、有機発光層よりむしろ発光マイクロLEDデバイスを受容するように変更された、 一実施形態が例示される。図3Aはある一実施形態に係るアクティブマトリクス型ディス プレイパネルの上面視の図であり、図3Bは、本発明のある実施形態に係る、図3Aのア クティブマトリクス型ディスプレイパネルの X - X 線及び Y - Y 線による、側面視の図で ある。かかる実施形態において、基本TFT基板102は、作動回路(例えば、T1、T 2)及び平坦化層122を含む図1~図2に関連して記述された典型的なAMOLEDバ ックプレーン内のものと同様であり得る。開口131は、作動回路に接触するよう平坦化 層122内に形成され得る。作動回路は、切替トランジスタ、駆動トランジスタ、及び蓄 積キャパシタを含む伝統的な2T1C(トランジスタ2つ、キャパシタ1つ)回路を含み 得る。2 T1 C回路が例示的であることを意図し、他の種類の回路又は伝統的な2 T1 C 回路の変更例が本発明の実施形態によって検討されるものと理解すべきである。例えば、 より複雑な回路は、駆動トランジスタ及び発光デバイスのプロセスのばらつき、又はそれ らの不安定さを補うために使用され得る。更に、本発明の実施形態はTFT基板102に おけるトップゲート型トランジスタ構造に関連して記述及び例示されるが、本発明の実施 形態はまた、ボトムゲート型トランジスタ構造の使用も検討する。同様に、本発明の実施 形態は、トップエミッション構造に関連して記述及び例示されるが、本発明の実施形態は また、ボトム、又はトップ及びボトムエミッション構造の使用も検討する。また、本発明 の実施形態は、接地タイライン及び接地リングを含むハイサイド駆動構成に関連して、以 下に具体的に記述及び例示される。ハイサイド駆動構成において、LEDは、回路が電流 をLEDのp端子から押し出すように、PMOS駆動トランジスタのドレイン側又はNM OS駆動トランジスタのソース側に存在し得る。本発明の実施形態はこれに限定されるも のではなく、接地タイライン及び接地リングがパネルにおける電力ラインとなり、電流が LEDのn端子を介して引き出される、ローサイド駆動構成で実施されてもよい。

#### [0030]

バンク開口148を含む、パターン化されたバンク層126は、その後平坦化層122の上部に形成される。バンク層126は、インクジェット印刷、スクリーン印刷、ラミネーション、スピンコーティング、CVD、及びPVD等の様々な技術によって形成され得る。バンク層126は、可視波長に対して、不透光性、透光性、又は半透光性を有してもよい。バンク層126は、光画定可能なアクリル、フォトレジスト、シリコン酸化物(SiO₂)、シリコン窒化物(SiNҳ)、ポリ(メチルメタクリレート)(PMMA)、ベンゾシクロブテン(BCB)、ポリイミド、アクリレート、エポキシ、及びポリエステル等であるが、それに限定されない、様々な絶縁体により形成される。一実施形態では、バンク層は、ブラックマトリクス材等の不透明材により形成される。例示的な絶縁性ブラックマトリクス材は、有機樹脂、ガラスペースト、及び黒色顔料、ニッケル、アルミニウム、モリブデン、及びそれらの合金等の金属粒子を含む樹脂若しくはペースト、金属酸化物粒子(例えば、クロム酸化物)、又は金属窒化物粒子(例えば、クロム窒化物)を含む

### [0031]

本発明の実施形態によれば、下記の図に関連して記述されるバンク層 1 2 6 の厚さ及びバンク開口 1 2 8 の幅は、開口内に実装されるマイクロLEDデバイスの高さ、マイクロLEDデバイスを転写する転写ヘッドの高さ、及び解像度に依存し得る。一実施形態では、ディスプレイパネルの解像度、画素濃度、及びサブ画素濃度は、バンク開口 1 2 8 の幅を構成し得る。40 P P I (インチ毎画素)及び 2 1 1 μ m サブ画素ピッチの例示的な 5 5 インチテレビの場合、バンク開口 1 2 8 の幅は、例示的な 5 μ m 幅のバンク周囲構造を構成するために数ミクロンから 2 0 6 μ m の範囲内であり得る。 4 4 0 P P I 及び 1 9 μ m サブ画素ピッチの例示的なディスプレイパネルの場合、バンク開口 1 2 8 の幅は、例示

的な  $5~\mu$  m幅のバンク周囲構造を構成するために数ミクロンから  $1~4~\mu$  mの範囲内であり得る。バンク構造の幅(例えば、バンク開口 1~2~8 間)は、その構造が必要とされるプロセスをサポートし、必要とされる P~P~I に対しスケーラブルである限りにおいて、いかなる適切なサイズであってもよい。

### [0032]

本発明の実施形態によれば、バンク層 1 2 6 の厚さは、バンク構造が機能するのに厚すぎない。厚さは、マイクロ L E D デバイスの高さ及び所定の視野角により決定してもよい。例えば、バンク開口 1 2 8 の側壁が平坦化層 1 2 2 に対して角度をなす場合、浅い角度ほどシステムのより広い視野角と相関し得る。一実施形態において、バンク層 1 2 6 の例示的な厚さは、 1  $\mu$  m から 5 0  $\mu$  m の間となり得る。

#### [0033]

パターン化された導電層がその後、パターン化されたバンク層126の上部に形成される。図3Bに戻ると、一実施形態では、パターン化された導電層は、バンク開口148内に作動回路と電気的に接触して形成された下部電極142を含む。パターン化された導電層はまた、任意的に、接地タイライン144及び/又は接地リング116を含んでもよい。本明細書内で使用されるように、接地「リング」という言葉は、円形パターン、すなわち対象物を完全に取り囲むパターン、である必要はない。むしろ、接地「リング」という言葉は、少なくとも部分的に画素エリアの3辺を囲むパターンを意味する。また、下記の実施形態は接地リング116に関連して記述及び例示される一方、本発明の実施形態はまた画素エリアの1辺(例えば、左、右、下、上)又は2辺(左、右、下、上のうちの2つの組み合わせ)に沿って走る接地ラインでも実施され得ることを理解すべきである。したがって、以下の記述において、接地リングの参照及び例示は、システム要求が許容する接地ラインと潜在的に置き換えられ得ることを理解すべきである。

#### [0034]

パターン化された導電層は、数多くの導電性及び反射性の材料により形成されてもよく 、かつ1層より多い層を含み得る。一実施形態において、パターン化された導電層は、ア ルミニウム、モリブデン、チタニウム、タングステン化チタン、銀、金、又はそれらの合 金等の金属膜から成る。パターン化された導電層は、アモルファスシリコン、インジウム スズ酸化物(ITO)及びインジウム亜鉛酸化物(IZO)等の透明導電性酸化物(TC O)、カーボンナノチューブ膜、又はポリ(3、4-エチレンジオキシチオフェン)(P EDOT)、ポリアニリン、ポリアセチレン、ポリピロール、及びポリチオフェン等の透 明導電性ポリマーを含み得る。一実施形態において、パターン化された導電層は、導電性 材料及び反射性の導電性材料の積層から成る。一実施形態において、パターン化された導 電層は、上部及び下部層並びに反射性の中間層を含む3層積層を含み、上部及び下部層の うちの一方又は両方は透明である。一実施形態において、パターン化された導電層は、導 電性酸化物 - 反射性金属 - 導電性酸化物の 3 層の積層から成る。導電性酸化物層は、透明 であってよい。例えば、パターン化された導電層は、ITO-銀-ITOの積層から成っ てもよい。かかる構成において、上部及び下部のITO層は、反射性金属(銀)層の拡散 及び/又は酸化を防ぎ得る。一実施形態において、パターン化された導電層は、Ti-A 1 - Tiの積層、又はMo - Al - Mo - ITOの積層から成る。一実施形態において、 パターン化された導電層は、ITO-Ti-A1-Ti-ITOの積層から成る。一実施 形態において、パターン化された導電層は、1μm以下の厚さである。パターン化された 導電層は、PVD等であるが、それに限定されない、適切な技術により積層され得る。

## [0035]

下部電極142、接地タイライン144、及び接地リング116の形成に続き、その後任意的に、パターン化された導電層の側壁を覆うTFT基板102の上部に絶縁層146が形成され得る。絶縁層146は、下部電極142、接地タイライン144、及び/又は接地リング116を形成するバンク層126及び反射層を少なくとも部分的に覆ってもよい。例示の実施形態において、絶縁層146は接地リング116を完全覆っているが、これは任意選択である。

10

20

30

20

30

40

50

#### [0036]

一実施形態において、絶縁層146は、ラミネーション、スピンコーティング、CVD、及びPVD等の適切な技術によるブランケット蒸着により形成され、その後、下部極142を露出させる開口及び接地タイライン149を露出させる開口149を形成するリソグラフィー等の適切な技術によりパターン化される。一実施形態では、リソグラフィーを必要とせず、絶縁層146及び開口149を形成するのにインクジェット印刷又はスクリーン印刷が使用され得る。絶縁層146は、SiO2、SiNx、PMMA、BCB、ポリイミド、アクリレート、エポキシ、及びポリエステル等であるが、それに限定されない、様々な材料により形成され得る。例えば、絶縁層146は、0.5μmの厚さであってよい。絶縁層146が、完全なシステムの発光の抽出が著しく低下しないように、バカコ128内の下部電極142の側壁の反射層の上部に形成され、透明又は半透明であってよい。絶縁層146の厚さはまた、光抽出効率を高めるよう、また発光デバイスのアイの反射性バンク構造への転写の間、転写ヘッドアレイを干渉しないよう、制御され得る。以下の記述においてより明らかにされるように、パターン化された導電層146は任意選択であり、導電層を電気的に分離させるための1つの方法を示す。

#### [0037]

図3Bに例示される実施形態において、下部電極142、接地タイライン144、及び 接地リング116は、同一の導電層で形成され得る。別の実施形態において、接地タイラ イン144及び/又は接地リング116は、下部電極142とは異なる導電性材料により 形成され得る。例えば、接地タイライン14及び接地リング116は、下部電極142よ り高導電性の材料により形成されてもよい。別の実施形態において、接地タイライン14 及び/又は接地リング116はまた、下部電極とは異なる層内に形成され得る。図3C~ 図3Dは、接地タイライン144及び接地リング116が、パターン化されたバンク層1 26内又はその下部に形成され得る、実施形態を示す。例えば、図3Cに例示する実施形 態では、開口149、130は、接地タイライン144及び接地リング116を形成する 時に、パターン化されたバンク層126を通して形成され得る。図3Dに例示する実施形 態において、開口149は接地タイライン144に接触するように、パターン化されたバ ンク層126及び平坦化層122を通して形成され得る。本実施形態において、例示され た開口は、接地リングを露出させるために形成されるのではないが、他の実施形態におい ては、開口は接地リングを露出させるために形成され得る。図3Dに例示する実施形態に おいて、接地リング及び接地タイライン144は、TFT基板102の作動回路を形成す る間に形成されたであろう。かかる実施形態において、下部電極142を形成するために 使用される導電層はまた、任意的に、開口149を通して接地タイライン144で形成さ れることになる上部電極層の電気的接触を更に可能にするための、ビア開口層145を含 み得る。したがって、図3A~図3Dに例示する実施形態は限定的でなく、数多くの可能 性が、開口149、130だけでなく、接地タイライン144及び接地リング116の形 成のためにも存在する、ということを理解すべきである。

### [0038]

図3A~図3Dに例示する実施形態を更に参照すると、複数の接合層140は、マイクロLEDデバイスの接合を促進するために下部電極層142上に形成されてもよい。例示される特定の実施形態において、2つの接合層140は、2つのマイクロLEDデバイスを接合するために例示される。一実施形態において、接合層140は、米国特許出願番号13/749,647に記載されるように、共晶合金接合、過渡的液相接合、又は固相拡散接合等の、接合機構を通してマイクロLEDデバイス上の(配置されることになっている)接合層で相互拡散される能力のために選択される。一実施形態において、接合層140は溶融温度が250 以下である。例えば、接合層140は、スズ(232 )、インジウム(156.7 )、又はそれらの合金等のはんだ材料を含み得る。接合層140はまた、幅よりも高さが大きい、柱形状であってもよい。本発明のいくつかの実施形態によれば、接合層140が高ければ、マイクロLEDデバイスの転写動作の間、TFT基板を備えたマイクロLEDデバイスのアレイの平坦度等の、システム部品のレベリング、及び

20

30

40

50

共晶合金接合及び過渡的液相接合の間等の接合の間、液化した接合層が表面の上部に拡散するため接合層の高さが変わることによる、マイクロLEDデバイスの高さのばらつき、において更なる自由度を提供し得る。接合層140の幅は、マイクロLEDの側壁の周囲の接合層140のウィッキング及び量子井戸構造の短絡を防ぐため、マイクロLEDの底面の幅よりも小さくてよい。

## [0039]

接合層140に加えて、図3A~図3Dに例示される実施形態は、マイクロLEDデバイスを受容するのに十分な大きさの各バンク開口128内に修復接合部位401を含み得る。このように、複数の接合層140及び修復接合部位401は、各バンク開口128内に冗長性及び修復構成を作る。図3A~図3Dに例示する特定の実施形態において、修復接合部位401は、下部電極層142上の露出面として例示される。しかし、本発明の実施形態は、これに限定されるものではない。他の実施形態において、修復接合部位401はまた、既存の冗長性スキームのために記載及び例示される他の2つの接合層140と同様の接合層140を含み得る。したがって、いくつかの実施形態において、接合層140は、修復部位401だけでなく、冗長性スキームにおける意図されたすべてのマイクロLEDデバイスの部位の下部電極層142上に設けられる。

#### [0040]

例示の実施形態において、接地タイライン144の配置は、ディスプレイパネル100の画素エリア104内のバンク開口128間に走り得る。また、複数の開口149は、複数の接地タイライン144を露出させる。開口149の数は、バンク開口128の列(上から下へ)の数と1:1の相関関係を持ってよいし、持たなくてもよい。例えば、図3Aに例示する実施形態において、接地タイ開口149は、バンク開口128の各列に対して形成されるが、これは必要ではなく、接地タイ開口149の数はバンク開口128の列の数より大きくてもよいし又は小さくてもよい。同様に、接地タイライン144の数は、バンク開口の行(左から右へ)の数と1:1の相関関係を持ってよいし、持たなくてもよい。例えば、例示の実施形態において、接地タイライン144は、バンク開口128の1行置きに形成されるが、これは必要ではなく、接地タイライン144の数はバンク開口128の行の数(n)と1:1の相関関係、又は任意の1:nの相関関係を持ってよい。

## [0041]

上記の実施形態では、接地タイライン144がディスプレイパネル100を左から右へ水平に横切って走るように記載及び例示されたが、実施形態はこれに限定されない。他の実施形態において、接地タイラインは、垂直に走ってもよく、又は格子を形成するよに水平及び垂直の両方に走ってもよい。数多くのあり得る変更例は、本発明の実施形態によって構想される。図1~図2に関連して前に例示及び記載されたようなAMOLED構成の動作により、接地リング116により近い、画素エリアの縁のサブ画素からの発光が薄して、画素エリアの中心の、接地リング116から最も遠いサブ画素からの発光が薄して、画素エリアの中心の、接地リング116次は表ができる。本発明の実施形態によれば、接地タイラインは、画素エリアのバに印に短気的に接続される。このように、接地信号は、サブ画素のマトリクスにより均一に印かた電気的に接続される。このように、接地信号は、サブ画素のマトリクスにより均一に印かたまた、接地タイライン144を(形成されることになっている)上部電極層より優れた電気伝導率を有する材料から形成することにより、電気接地経路における接触抵抗を減らすことができる。

## [0042]

図4A~図4Hは、本発明の一実施形態に係る、TFT基板102にマイクロLEDデバイスのアレイを転写する方法のための側断面視の図である。図4Aを参照すると、転写ヘッド基板300に支持される転写ヘッド302のアレイは、キャリア基板200上に支持されるマイクロLEDデバイス400のアレイの上部に位置する。ヒーター306及び熱分配板304は、任意的に、転写ヘッド基板300に付着される。ヒーター204及び熱分配板202は、任意的に、キャリア基板200に付着される。図4Bに示すように、

20

30

40

50

マイクロLEDデバイス400のアレイは、転写ヘッド302のアレイに接触し、図4Cに示すように、キャリア基板200からピックアップされる。一実施形態において、マイクロLEDデバイス400のアレイは、静電的な原理に従い動作する転写ヘッド302のアレイでピックアップされる、すなわち、それらは静電転写ヘッドである。

### [0043]

図4 D は、本発明の一実施形態に係る、TFT基板 1 0 2 の上部にマイクロLEDデバイス 4 0 0 を保持する転写ヘッド 3 0 2 の側断面視の図である。例示の実施形態において、転写ヘッド 3 0 2 は、転写ヘッド基板 3 0 0 に支持される。上述のように、ヒーター 3 0 6 及び熱分配板 3 0 4 は、任意的に、熱を転写ヘッド 3 0 2 に印加するために転写ヘッド基板に付着されてもよい。ヒーター 1 5 2 及び熱分配板 1 5 0 はまた、或いは代替的に、任意的に、TFT基板 1 0 2 及び / 又は下記のマイクロLEDデバイス 4 0 0 上の任意選択の接合層 4 1 0 上の接合層 1 4 0 に熱を転写するのに使用され得る。

#### [0044]

図4Dを更に参照すると、例示のマイクロLEDデバイス400のクローズアップ図が 、ある実施形態に従って示される。例示される特定のマイクロLEDデバイス400は例 示であり、本発明の実施形態が限定されないことを理解すべきである。例示される特定の 実施形態において、マイクロLEDデバイス400は、マイクロp-nダイオード450 及び下部導電性接触部420を含む。接合層410は、任意的に、下部導電性接触部42 0の下部に形成されてもよく、下部導電性接触部 4 2 0 は、マイクロ p - n ダイオード 4 5 0 と接合層410 との間にある。一実施形態において、マイクロLEDデバイス400 は、上部導電性接触部452を更に含む。一実施形態において、マイクロp - n ダイオー ド 4 5 0 は、上部 n ドープ層 4 1 4 、 1 つ以上の量子井戸層 4 1 6 、及び下部 p ドープ層 4 1 8 を含んでいる。他の実施形態において、 n ドープ層及び p ドープ層の配置が逆とな り得る。マイクロ p - n ダイオードは、直立の側壁又はテーパ形状の側壁を有するように 製造することができる。特定の実施形態において、マイクロp-nダイオード450は、 外向きに(上部から底部へ)テーパ形状の側壁453を有している。特定の実施形態にお いて、マイクロp-nダイオード450は、内向きに(上部から底部へ)テーパ形状の側 壁を有している。上部及び下部導電性接触部420、452。例えば、下部導電性接触部 4 2 0 は、電極層、及び電極層と任意選択の接合層 4 1 0 との間のバリア層を含むことが できる。上部及び下部導電性接触部420、452は、可視波長範囲(例えば、380n m~750nm)に対し透光性、又は不透光性であってよい。上部及び下部導電性接触部 4 2 0 、 4 5 2 は、任意的に、銀層等の反射層を含み得る。マイクロp - n ダイオード及 び導電性接触部は各々、上面、底面、及び側壁を有することができる。一実施形態におい て、マイクロp - nダイオード450の底面451は、マイクロp - nダイオードの上面 よりも広く、側壁453は上部から底部へと外向きにテーパ形状である。マイクロp-n ダイオード 4 5 0 の上面は、 p ・n ダイオードの底面よりも広くてもよく、又はほぼ同じ 幅であってもよい。一実施形態において、マイクロp-nダイオード450の底面451 は、下部導電性接触部420の上面よりも広い。マイクロp-nダイオードの底面はまた 、下部導電性接触部420の上面とほぼ同じ幅であってもよい。一実施形態において、マ イクロρ - n ダイオード 4 5 0 は、 3 μ m 又は 5 μ m のように数ミクロンの厚さ、導電性 接触部420、452は、0.1 μ m ~ 2 μ m の厚さ、及び任意選択の接合層410は、 0 . 1 μ m ~ 1 μ m の厚さである。一実施形態において、各マイクロLEDデバイス40 0の最大幅は、1~100μm、例えば、30μm、10μm、又は5μmである。一実 施形態において、各マイクロLEDデバイス400の最大幅は、ディスプレイパネルの特 定の解像度及びPPIのためのバンク開口128における可能なスペースと適合しなけれ ばならない。

#### [0045]

図4 E は、本発明の実施形態に係る、TFT基板 1 0 2 の上部にアレイマイクロLEDデバイス 4 0 0 を保持する転写ヘッドのアレイの側断面視の図である。図4 E は、図 4 D に例示する構造とほぼ同様であるが、主要な違いは、マイクロLEDデバイスのアレイ内

(15)

の単一のマイクロLEDデバイスに対してマイクロLEDデバイスのアレイの転写が示されている点である。

## [0046]

次に図4Fを参照すると、TFT基板102は、マイクロLEDデバイス400のアレイと接触している。例示の実施形態において、TFT基板102がマイクロLEDデバイス400のアレイと接触することは、接合層140が対応する各マイクロLEDデバイスに対してマイクロLEDデバイス接合層410と接触することを含む。一実施形態において、各マイクロLEDデバイス接合層410は、対応する接合層140よりも幅広である。一実施形態において、マイクロLEDデバイス400のアレイをTFT基板102に接合するために、エネルギーが静電転写ヘッドアセンブリーから及びマイクロLEDデバイス400のアレイを通して伝達される。例えば、共晶合金接合、過渡的液相接合、及び固相拡散接合等の、数種類の接合機熱を促進するために、熱エネルギーが伝達され得る。熱エネルギーの伝達はまた、静電転写ヘッドアセンブリーから圧力をかけることに付随し得る。

#### [0047]

図4 Gを参照すると、一実施形態において、熱伝達は接合層 1 4 0 を液化する。液化した接合層 1 4 0 は、クッションとして作用し、接合の間、マイクロLEDデバイス 4 0 0 のアレイとTFT基板との間のシステムの不均一なレベリング(例えば、平面でない表面)、及びマイクロLEDデバイスの高さのバラツキを、部分的に補償し得る。過渡的液相接合の特定の実施において、液化された接合層 1 4 0 は、金属間化合物層を、接合層 1 4 0 の周囲溶融温度より高い周囲溶融温度で形成するために、マイクロLEDデバイス接合層 4 1 0 と相互拡散する。したがって、過渡的液相接合は、接合層の最低液体相温度以上で達成され得る。本発明のいくつかの実施形態において、マイクロLEDデバイス接合層 4 1 0 は、ビスマス(2 7 1 . 4 ))等の 2 5 0 を越える溶融温度又は金(1 0 6 4 )、銅(1 0 8 4 )、銀(9 6 2 )、アルミニウム(6 6 0 )、亜鉛(4 1 9 . 5 )、ニッケル(1 4 5 3 )等の 3 5 0 を越える溶融温度の材料により形成され、TFT基板接合層 1 4 0 は、スズ(2 3 2 )又はインジウム(1 5 6 . 7 )等の 2 5 0 未満の溶融温度である。

### [0048]

このように、TFT基板102を支持する基板150は、接合層140の溶融温度未満の温度まで加熱することができ、転写ヘッドのアレイを支持する基板304は、接合層410の溶融温度未満であるが接合層140の溶融温度を越える温度まで加熱される。かかる実施形態において、静電転写ヘッドアセンブリーからマイクロLEDデバイス400のアレイを通して熱を転写することは、金属間化合物として後続の等温凝固で接合層140の過渡的液体状態を形成するのに十分である。液相において、低溶融温度材料は表面の上部に拡散すると共に高溶融温度材料の固溶体に拡散又は高溶融温度材料を分解すると共に金属間化合物として固体化される。特定の実施形態において、転写ヘッドのアレイを支持する基板304は180 で保持され、接合層410は金により形成され、接合層140はインジウムにより形成される。

### [0049]

マイクロLEDデバイス400のアレイをTFT基板に接合するためにエネルギーを伝達することに続き、マイクロLEDデバイス400のアレイは収容基板上にリリースされ、静電転写ヘッドのアレイは、図4Hに示すように、離される。マイクロLEDデバイス400をリリースするのは、静電電圧源をオフにする、静電転写ヘッド電極に印加される電圧を下げる、交流電圧の波形を変える、及び電圧源を接地することを含む、様々な方法で達成され得る。

#### [0050]

次に図5A~図5Fを参照すると、マイクロLEDデバイス400のアレイの異なる色の発光での一連の転写は、本発明の実施形態によって例示される。図5Aに例示する特定の構成において、第1の転写手順は、赤色発光マイクロLEDデバイス400Rのアレイ

10

20

30

40

20

30

40

50

を第1のキャリア基板からTFT基板102へ転写するために完了している。例えば、マ イクロLEDデバイス400Rが赤色光(例えば、波長が620~750nm)を発光す るように設計される場合、マイクロp-nダイオード450は、ひ化アルミニウムガリウ ム(AlGaAs)、ひ化リン化ガリウム(GaAsP)、リン化インジウムアルミニウ ムガリウム (AlGaInP)、リン化ガリウム (GaP) 等の材料を含み得る。図5B を参照すると、第2の転写手順は、赤色発光マイクロLEDデバイス400Rの冗長アレ イを転写するために完了している。例えば、冗長アレイは、異なるキャリア基板から、す なわち、第1のキャリア基板の異なるエリア(例えば、対向する側から、異なるエリアは 重ならず、又は無作為抽出)から、第2のアレイが第1のキャリア基板の同じ相関のある 欠陥エリア又は汚損エリア(例えば、粒状物)から転写する可能性を減じるために、転写 され得る。このように、2つの相関のないエリアから転写することにより、欠陥のある2 つのマイクロLEDデバイス400を同じバンク構造128に転写する可能性を減じるこ とが可能であり、又は代替的に、マイクロLEDデバイス400を単一のバンク構造12 8へ転写しないことにより、キャリア基板の欠陥のある又は汚損されたエリア内のマイク 口LEDデバイスをピックアップすることは不可能であったためである。更に別の実施形 態において、2つの異なるウェハからの冗長アレイを使用することにより、両色の混合を 取得し、ディスプレイの平均電力消費量を異なるウェハにおけるマイクロLEDデバイス の主要な発光波長の既存の知識に基づいて調整することが可能であり得る。例えば、第一 のウェハが第1の電力消費量において平均赤色発光が630nmであると知られているの に対し、第2のウェハは第2の電力消費量において平均赤色発光が610発光であると知 られている場合、冗長アレイは、平均電力消費量又は交互色域を得る両ウェハからのマイ クロ L E D デバイスからなり得る。

### [0051]

図5 Cを参照すると、第3の転写手順は、緑色発光マイクロLEDデバイス400Gのアレイを第2のキャリア基板からTFT基板102へ転写するために完了している。例えば、マイクロLEDデバイス400Gが緑色光(例えば、波長が495~570nm)を発光するように設計される場合、マイクロp・nダイオード450は、窒化インジウムガリウム(InGaN)、窒化ガリウム(GaN)、リン化ガリウム(GaP)、リン化インジウムアルミニウムガリウム(A1GaInP)、及びリン化アルミニウムガリウム(A1GaP)等の材料を含み得る。緑色発光マイクロLEDデバイス400Gの冗長アレイを転写する第4の転写手順は、前記と同様に、図5口に示される。

## [0052]

図5 Eを参照すると、第5の転写手順は、青色発光マイクロLEDデバイス400Bのアレイが第3のキャリア基板からTFT基板102へ転写するために完了している。例えば、マイクロLEDデバイス400Bが青色光(例えば、波長が450~495nm)を発光するように設計される場合、マイクロp-nダイオード450は、窒化ガリウム(GaN)、窒化インジウムガリウム(InGaN)、及びセレン化亜鉛(ZnSe)等の材料を含み得る。青色発光マイクロLEDデバイス400Bの冗長アレイを転写する第6の転写手順は、前記と同様に、図5Fに示される。

#### [0053]

図5 A ~ 図5 F に関連して上述される特定の実施形態において、各サブ画素の第1及び第2のマイクロLEDデバイス400は、別個に転写される。例えば、これにより、相関のある欠陥の可能性を減じることができる。しかし、他の実施形態において、第1及び第2のマイクロLEDデバイスを同じキャリア基板から同時に転写することが可能である。このように、同時転写は、生産スループットを増加させることができるが、マイクロLEDデバイスをキャリア基板の同じエリアから転写するため、相関のある欠陥の可能性を犠牲にして、冗長性スキームの利点のいくつかを依然として提供する。かかる実施形態において、処理シーケンスは図5 B、図5 D、図5 Fの順のシーケンスに類似するであろう。

### [0054]

本発明の実施形態によれば、転写ヘッドは画素又はサブ画素のアレイに対応するバック

20

30

40

50

プレーン上のバンク開口のピッチに合致するピッチ(× , y、及び / 又は対角線)により分けられる。表1は、解像度1920×1080p及び2560×1600の様々な赤-緑-青(RGB)ディスプレイのための本発明の実施形態に従う例示的な実施のリストを提供する。本発明の実施形態は、RGBカラースキーム又は解像度1920×1080p若しくは2560×1600に限定されず、特定の解像度及びRGBカラースキームは単に例示の目的のためのものであることを理解すべきである。

# 【表1】 表1

| 表示基板            | 画素ピッチ       | サブ画素ピッチ     | インチ毎画素 | 可能な転写ヘッドアレ        |

|-----------------|-------------|-------------|--------|-------------------|

|                 | (x, y)      | (x, y)      | (PPI)  | イピッチ              |

| 55インチ           | (6 3 4 μ m, | (2 1 1 μ m, | 4 0    | X : 2 1 1 μ m の倍数 |

| $1920 \times 1$ | 6 3 4 μ m)  | 6 3 4 μ m)  |        | 又は分数              |

| 080             |             |             |        | Y:634μmの倍数        |

|                 |             |             |        | 又は分数              |

| 10インチ           | (85 μm, 8   | (28 μm, 8   | 299    | X:28μmの倍数又        |

| $2560 \times 1$ | 5 μ m)      | 5 μ m)      |        | は分数               |

| 600             |             |             |        | Y:85μmの倍数又        |

|                 |             |             |        | は分数               |

| 4インチ            | (78 μm, 7   | (26 μm, 7   | 3 2 6  | X:26μmの倍数又        |

| 6 4 0 × 1 1     | 8 μ m)      | 8 μ m)      |        | は分数               |

| 3 6             |             |             |        | Y:78μmの倍数又        |

|                 |             |             |        | は分数               |

| 5インチ            | (58 μ m, 5  | (19 μm, 5   | 4 4 0  | X : 1 9 μ mの倍数又   |

| $1920 \times 1$ | 8 μ m)      | 8 μ m)      |        | は分数               |

| 080             |             |             |        | Y:58μmの倍数又        |

|                 |             |             |        | は分数               |

### [0055]

上記の例示の実施形態において、40PPI 画素濃度は、557 ンチ、解像度 1920 × 1080 pのテレビに対応することができ、326 及び 440 PPI 画素濃度は、RETINA(登録商標)ディスプレイを備えたハンドヘルドデバイスに対応することができる。本発明の実施形態によれば、数千、数百万、又は何億もの転写ヘッドでさえ、マイクロピックアップアレイのサイズにより、物質移動ツールのマイクロピックアップアレイ内に含まれ得る。本発明の実施形態において、転写ヘッドの $1cm \times 1.12cm$  のアレイは、 $211\mu$ m、 $634\mu$ mピッチの837 転写ヘッド及び $19\mu$ m、 $58\mu$ mピッチの102,000 転写ヘッドを含み得る。

#### [0056]

転写ヘッドのアレイでピックアップされるマイクロLEDデバイスの数は、転写ヘッドのピッチに合致してもよく、合致しなくてもよい。例えば、19μmのピッチにより分離される転写ヘッドのアレイは、19μmのピッチでマイクロLEDデバイスのアレイをピックアップする。別の実施例において、19μmのピッチにより分離される転写ヘッドのアレイは、約6.33μmのピッチでマイクロLEDデバイスのアレイをピックアップする。このように、転写ヘッドは、バックプレーンへの転写のために2つ置きのマイクロLEDデバイスをピックアップする。いくつかの実施形態によれば、発光マイクロデバイスのアレイの上面は、マイクロLEDデバイスをバンク開口内に配置する間、転写ヘッドがバックプレーン上の絶縁層(又はいかなる介在層)により損傷されること又は絶縁層(又はいかなる介在層)を損傷することを防ぐために、絶縁層の上面より高い。

#### [0057]

図6Aは、上部電極層の形成後の、一実施形態によるアクティブマトリクス型ディスプ

20

30

40

50

レイパネルの上面視の図である。図6Bは、別個の上部電極層の形成後の、一実施形態によるアクティブマトリクス型ディスプレイパネルの上面視の図である。図6C~図6Dは、本発明の実施形態に係る、図6A又は図6Bのいずれかのアクティブマトリクス型ディスプレイパネルのX・X線及びY・Y線による、側面視の図である。図6A~図6Bに例示する実施形態によれば、1つ以上の上部電極層118は、画素エリア104内のバンク開口128間を走る接地タイライン144と電気的に接触して開口149内に形成されると共に、マイクロLEDデバイス400のアレイを含む画素エリア104の上部に形成される。

## [0058]

次に図6C~図6Dを参照すると、1つ以上の上部電極層118を形成する前に、マイ クロLEDデバイス400は、上部及び下部電極層118、142間の電気的短絡、又は 1つ以上の量子井戸416における短絡を防ぐために、バンク開口128内にパッシベー トされる。例示のように、アレイマイクロLEDデバイス400の転写の後、パッシベー ション層148はバンク開口128のアレイ内のマイクロLEDデバイス400の側壁の 周囲に形成されてもよい。一実施形態において、マイクロLEDデバイス400が垂直L EDデバイスである場合、パッシベーション層148は量子井戸構造416を覆いそれを 補う。パッシベーション層148はまた、短絡の可能性を防ぐため、任意選択の絶縁層1 46によりまだ覆われていない下部電極層142のいずれかの部分を覆ってもよい。した がって、パッシベーション層148は、下部電極層142だけでなく、量子井戸構造41 6 もまたパッシベートするために使用され得る。本発明の実施形態によれば、パッシベー ション層 1 4 8 は、上部導電性接触部 4 5 2 等の、マイクロLEDデバイス 4 0 0 の上面 には形成されない。一実施形態において、プラズマエッチング処理、例えば、O。又はC F<sub>4</sub>プラズマエッチングは、上部導電性接触部452等のマイクロLEDデバイス400 の上面を、上部導電性電極118層118がマイクロLEDデバイス400と電気的に接 触できるように、露出させるようにした上で、パッシベーション層148をエッチバック するためにパッシベーション層148を形成した後に使用され得る。

#### [0059]

本発明の実施形態によれば、パッシベーション層148は、完成されたシステムの光抽出効率を著しく低下させないために、可視波長に対して透光性又は半透光性であってよい。パッシベーション層は、エポキシ、ポリ(メチルメタクリレート)(PMMA)等のアクリル(ポリアクリレート)、ベンゾシクロブテン(BCB)、ポリイミド、及びポリエステル等であるが、それに限定されない、様々な材料で形成されてもよい。一実施形態において、パッシベーション層148は、インクジェット印刷又はスクリーン印刷により、マイクロLEDデバイス400の周囲に形成される。

## [0060]

図6Cに例示する特定の実施形態において、パッシベーション層148は、バンク開口128内にのみ形成される。しかし、これは必要とされるものではなく、パッシベーション層148は、バンク構造層126の上部に形成されてもよい。更に、絶縁層146の形成は必要とされず、パッシベーション層148はまた、導電層を電気的に絶縁するために使用され得る。図6Dに例示する実施形態に示すように、パッシベーション層148はまた、下部電極142及び接地タイライン144を形成する導電層の側壁をパッシベートするために使用してもよい。一部の実施形態では、パッシベーション層148は、任意的に、接地リング116をパッシベートするために使用してもよい。いくつかの実施形態によれば、開口149の形成は、接地タインライン144の上部のパッシベーション層148をインクジェット印刷又はスクリーン印刷するプロセスの間に形成されてもよい。開口はまた、任意的に、接地リング116の上部に形成されてもよい。このように、別個のパターンニング動作は、開口を形成するために必要とされなくてもよい。

#### [0061]

本発明のいくつかの実施形態によれば、通路151、すなわち、井戸構造は、特にパッシベーション層148がインクジェット印刷又はスクリーン印刷等による溶媒系を使用し

20

30

40

50

て形成される時に、パッシベーション層148が過度に広がり、接地タイライン149の上部にオーバーフローするのをキャプチャ又は防ぐために、図6Cに示すように、バンク層126内に形成されてもよい。したがって、いくつかの実施形態において、通路151は、バンク開口128と、隣接する接地タイライン144との間の、バンク層126内に形成される。

## [0062]

図6C~図6Dを更に参照すると、パッシベーション層148の形成後、1つ以上の上 部導電電極層118が各マイクロLEDデバイス400の上部に、もし存在すれば上部接 触層452と電気的に接触して、形成される。以下の記述における特定の用途によっては 、上部電極層118は、可視波長に対して、不透光性、反射性、透光性、又は半透光性を 有してもよい。例えば、トップエミッションシステムにおいて、上部電極層118は、透 光性を有してもよく、ボトムエミッションシステムにおいては、上部電極層は反射性を有 してもよい。例示の透光性を有する導電材は、アモルファスシリコン、インジウムスズ酸 化物(ITO)及びインジウム亜鉛酸化物(IZO)等の透明導電性酸化物(TCO)、 カーボンナノチューブ膜、又はポリ(3、4-エチレンジオキシチオフェン)(PEDO T)、ポリアニリン、ポリアセチレン、ポリピロール、及びポリチオフェン等の透明導電 性ポリマーを含む。一実施形態において、上部電極層118は、銀、金、アルミニウム、 モリブデン、チタニウム、タングステン、ITO、及びIZO等のナノ粒子を含む。特定 の実施形態において、上部電極層118は、インクジェット印刷若しくはスクリーン印刷 ITO、又はPEDOT等の透明導電性ポリマーにより形成される。形成の他の方法は、 化学蒸着法(CVD)、物理蒸着法(PVD)、スピンコーティングを含み得る。上部電 極層118はまた、可視波長に対して反射性を有してもよい。一実施形態において、上部 導電電極層118は、アルミニウム、モリブデン、チタニウム、タングステン化チタン、 銀、金、又はそれらの合金等の反射性金属膜を含み、例えば、ボトムエミッションシステ ムにおいて使用される。

#### [0063]

本発明のいくつかの実施形態によれば、接地タイライン144は、上部電極層118よ り電気的により導電性を有してもよい。図3Dに例示する実施形態において、接地タイラ イン 1 4 4 は、TFT基板 1 0 2 内のトランジスタ ( 例えば、T 2 ) のうちの 1 つに対す るソース/ドレイン接続又はゲート電極を形成するのに使用される同一の金属層から形成 され得る。例えば、接地タイライン144は、銅又はアルミニウム、それらの合金を含む . 共通の相互接続材から形成され得る。図3B~図3C及び図6C~図6Dに例示する実 施形態において、接地タイライン144はまた、下部電極層142と同じ材料から形成さ れ得る。例えば、接地タイライン144及び下部電極層142は、層の導電性も改善し得 る、反射性材料を含む。特定の実施例において、接地タイライン144及び下部電極は、 金属膜又は金属粒子を含んでもよい。いくつかの実施形態によれば、上部電極層118は 、アモルファスシリコン等の透光性又は半透光性を有する材料、インジウムスズ酸化物( ITO)及びインジウム亜鉛酸化物(IZO)等の透明導電性酸化物(TCO)、カーボ ンナノチューブ膜、又はポリ(3、4-エチレンジオキシチオフェン)(PEDOT)、 ポリアニリン、ポリアセチレン、ポリピロール、及びポリチオフェン等の透明導電性ポリ マーにより形成されてもよく、これらのすべては、フィルム積層内の金属膜を含む導電性 及び反射性を有する下部電極層よりも、導電性が低くてもよい。

### [0064]

再び図6Aを参照すると、例示される特定の実施形態において、上部電極層118は、マイクロLEDデバイス400のアレイを含む画素エリア104の上部に形成される。上部電極層118はまた、存在する場合は開口149内に形成されてもよく、画素エリア104内のバンク開口128間を走る接地タイライン149に電気的に接触してもよい。かかる実施形態において、接地タイライン144は接地リング116に電気的に接触しているため、上部電極層118を画素エリア104外に形成する必要はない。例示のように、接地リング116は、絶縁層146、パッシベーション層148、又更にはバンク構造層

20

30

40

50

126若しくは平坦化層122等の電気的に絶縁する層の下に埋め込んでもよい。図6Aでは、上部電極層118を画素エリア104の上部にのみ含むよう、かつ接地タイライン144を含むように記述及び例示しているが、本発明の実施形態はこれに限定されない。例えば、接地タイライン144は、冗長性スキーム及び修復部位を設けるのに必要ではなく、また上部電極層を接地リング116又は接地ラインの上部にそれに電気的に接触するように形成しない必要もない。

#### [0065]

図6Bは、別個の上部電極層118が1つ以上のマイクロLEDデバイス400を1つ以上の接地タイライン144に接続するように形成される、代替の実施形態を示す。図6Bに例示する特定の実施形態において、上部電極層118は、マイクロLEDデバイス400から付近の接地タイライン144までの電気路を提供すればよい。したがって、上部電極層118が、そのために、全画素エリア104又は全バンク開口128でさえも覆う必要はない。例示の特定の実施形態において、各上部電極層118は、中間接地タイライン144の対向する側のバンク開口のペア内のマイクロLEDデバイス400を接続する。しかし、この特定の構成は例示であり、数多くの異なる構成が可能である。例えば、単一の上部電極層118は、接地タイライン又は接地リングまで、n行のマイクロLEDデバイス又はバンク開口128上に走り、電気的に接続してもよい。例示のように、上部電極層118は、接地タイライン144に対する開口149内に形成されてもよい。かかる実施形態において、接地タイライン144は接地リング116に電気的に接触しているため、上部電極層118を画素エリア104外に形成する必要はない。

### [0066]

例示のように、図6A~図6Bに示す実施形態に従って、接地リング116は、絶縁層146等の電気的に絶縁する層の下に埋め込んでもよい。図6Bに例示する特定の実施形態において、マイクロLEDデバイス400の最上行は、個別の上部電極層118で接地リング116に接続されるように例示される。かかる実施形態において、各上部電極層118は、上述のように、1つ以上の開口を通して接地リング116に接触する。したがって、図6A~図6Bに例示する実施形態は、マイクロLEDデバイス400を画素エリア104内の接地タイライン144に接続する1つの方法を提供するが、これは接地タイライン144を通さずに接地リング116に接続するために別個の上部電極層118を使用することを排除するものではない。

#### [0067]

図6A~図6Bに例示するように、上部電極層118の線幅は、用途によって変化し得る。例えば、線幅は画素エリア104の線幅に近づき得る。代替的に、線幅は最小となり得る。例えば、約15μmほどの狭い線幅は、市販のインクジェットプリンターにより実現され得、約30μmほどの狭い線幅は、市販のスクリーンプリンターにより実現され得る。したがって、上部電極層118の線幅は、マイクロLEDデバイスの最大幅より大きくてもよいし、小さくてもよい。

#### [0068]

別の態様において、本発明の実施形態は、インクジェット印刷又はスクリーン印刷で上部電極層118を局所的に形成するのに特に適し得る。特に、インクジェット印刷は非接触印刷法であるため、適し得る。図1~図2のディスプレイパネルの製造に使用されるような従来のAMOLEDバックプレーン処理シーケンスは、典型的に、各バックプレーン100をより大きな基板からシンギュレートすることに続き、上部電極層を蒸着チャンバ内にブランケット蒸着する。いくつかの実施形態によれば、ディスプレイパネル100のバックプレーンは、マイクロLEDデバイス400のアレイの転写に先立ち、より大きい基板からシンギュレートされる。一実施形態において、インクジェット印刷又はスクリーン印刷は、別個の各ディスプレイパネル100に対して別個のマスク層を必要とせずに、各上部電極層118をパターン化するための実用的なアプローチを提供する。

#### [0069]

図7は、本発明の一実施形態に係る冗長性及び修復部位構成を含むスマート画素ディス

プレイの上面視の概略図である。示されるように、ディスプレイパネル200は、基板201を含み、それは不透明、透明、硬質、又は柔軟であってもよい。スマート画素エリア206は、異なる発光色の別個のサブ画素、及びTFT基板に関連して上述した作動回路を含むマイクロコントローラチップ208を含んでもよい。このように、作動回路含むマイクロコントローラチップ208の両方は、基板201の同一側又は同一面に転写される。配電線は、マイクロコントローラチップ208を、TFT基板と同様に、データ駆動回路112に接続し得る。同様に、バンク層構造は、マイクロコントローラチップ208を、TFT基板と同様に、データ駆動回路110及びスキャン駆動回路112に接続し得る。同様に、バンク層構造は、マイクロしたのと同様に、基板201上に形成されてもよい。同様に、上部電極層118、マイクロしたのと同様に、基板201上に形成されてもよい。同様に、上部電極層118、マイクロしてのと同様に、基板201上に形成されてもよい。同様に、上部電極層118、マイクロに同様の冗長性及び修復部位構成は、TFT基板構成について上述したのと同様に、スマート画素構成で形成されてもよい。

#### [0070]

### [0071]

図8A~図8Bは、図5A~図5Fに示す転写作業等の、マイクロLEDデバイスのキャリア基板からディスプレイ基板への転写後、並びにパッシベーション層148及び上部電極層118の形成に先立ち、欠陥のある、欠落した、又は汚損されたマイクロLEDデバイスを検出するための、本発明の実施形態に係る、統合検査方法を示す。このように、欠陥のある、欠落した、又は汚損されたマイクロLEDデバイスの検出は、パッシベーション層148及び上部電極層118の蒸着パターンを潜在的に変更するため、及び必要であれば、潜在的に代替のマイクロLEDデバイスを転写するために、使用されてもよい。次に図8Aを参照すると、光源804及びカメラ806を支持するキャリッジ802は、下部電極層142に転写及び接合されたマイクロLEDデバイス400のアレイを担持するディスプレイ基板上でスキャンされる。

## [0072]

一実施形態において、カメラ806はラインスキャンカメラである。例えば、ラインスキャンカメラは、ラインスキャンカメラが撮像面上を通過する際に、画像を作成するフレームをつなげるコンピュータシステムに連続的に供給するために使用され得る一行の画素センサを、典型的に有する。一実施形態において、カメラ806は画素の×・y両方の次元を有する二次元(2D)カメラである。本発明の実施形態によれば、カメラ806は、例えば、最大幅1~100μmのマイクロLEDデバイス400を撮像可能な解像度を有するべきである。解像度は、画素センサにおける画素サイズにより決定でき、解像度を高めるために光学部品を使用することにより援助され得る。例として、一実施形態において

10

20

30

40

20

30

40

50

、マイクロLEDデバイス400は、最大幅約5 $\mu$ mである。ある例示的な、使用され得るラインスキャンカメラ806は、画素サイズが3.5 $\mu$ mのBASLER(登録商標)RUNNER SERIES САMERA(ドイツAhrensburgのBasler AG社から入手可能)である。光学部品の追加により、画素サイズが3.5 $\mu$ mの場合、約1.75 $\mu$ mまで解像度を許容しうる。ラインスキャンカメラはまた、それらのラインスキャン速度及びラインスキャン幅のために選択され得る。例えば、ラインスキャン速度は、毎秒数メートルまで達成することができ、ラインスキャン幅は一般的に10~50mmの間が可能である。

## [0073]

一実施形態において、光源804は、スキャンされる表面を照らすために使用される。例えば、一実施形態において、マイクロLEDデバイス400が意図された位置に置かれたかどうかを検証するために、カメラ806は、基板201、102の表面上にスキャンされる。このように、カメラ806は、各マイクロLEDデバイス400に対し、キャリア基板からディスプレイ基板201、102までの転写が成功したことを検出するために使用され得る。

#### [0074]

別の実施形態において、光源804は、マイクロLEDデバイス400の光ルミネッセンスを誘発するために光の励起波長を放出するために使用される。光源804は、LED照明又はエキシマレーザ等であるが、それに限定されない、様々な光源であってよい。このように、ラインスキャンカメラ808は、発光しない又は不規則な発光のどちらかである、マイクロLEDデバイス400からの特定の発光波長を検出するために使用され得る。したがって、この情報は、そうでなければキャリア基板上で容易に矯正することがでのよい、マイクロLEDデバイス400内の欠陥を検出するために使用され得る。上述のよい、マイクロLEDデバイス400内の欠陥を検出するために使用され得る。上述のマイクロLEDデバイス400を含み得る。様々な欠陥が、キャリア基板上のマイクロLEDデバイス400がキャリア基板上にある場合、それらを固別に大いないるマイクロLEDデバイス400がキャリア基板上にある場合、それらを個別にたいがある場合、本発明の実施形態に従い、ディスプレイ基板201、102上で冗長性スキーム又は修復部位で欠陥を矯正することが単により効果的であり得る。

## [0075]

一実施形態において、光源804は、マイクロLEDデバイスからの光のレッドシフト又は蛍光発光を誘発するために、対象のマイクロLEDデバイスが発光する光の波長よりも短い波長の光を発する。本発明の実施形態によれば、光源804は調整可能であり得る、又は所望の波長に設定された複数の光源が備えられる。例えば、励起波長500~600mmは、赤色発光マイクロLEDデバイス400Rからの赤色光(例えば、波長620~750mm)の発光を誘発するために使用されてもよく、励起波長430~470mmは、緑色発光マイクロLEDデバイス400Gからの緑色光(例えば、波長495~570mm)の発光を誘発するために使用されてもよく、励起波長325~425mmは、の発光を誘発するために使用されてもよく、励起波長325~425mmはの発光を誘発するために使用されてもよい。しかし、これらの範囲は例示であり、排他的ではない。いくつかの例では、選択された範囲の波長のみが検出されるように、ラインスキャンカメラ806の上部にカラーフィルタ808を設けることが役立つ場合がある。これにより、異なる色のマイクロLEDデバイスからの発光から生じる希釈を減じることができる。

#### [0076]

次に図8Bを参照すると、マイクロLEDデバイスのアレイの接合後に基板201、102をスキャンするための実施形態が例示される。かかる実施形態において、例示の基板は、幅約100mmであり、ラインスキャン幅約20mmのラインスキャンカメラが備え

20

30

40

50

られる。例示のように、基板201、102は、基板201、102の全面をカバーするのに全部で3つのパスによりスキャンされる。一実施形態において、ラインスキャンカメラ806は、マルチカラーカメラであり、光源(複数も可)204がすべてのマイクロLEDデバイスを励起するために必要な励起波長を提供すると仮定し、赤色、緑色、及び青色すべてのマイクロLEDデバイス400を同時に撮像可能である。別の実施形態において、特定のマイクロLEDデバイス発光色をターゲットにするために、単一の励起波長又は範囲のみが提供される。かかる実施形態において、すべてのマイクロLEDデバイス400を撮像するために3つの励起波長で、基板201、102を3回にわけてスキャンすることが必要となり得る。しかし、毎秒数メーターまでのラインスキャン速度では、複数のスキャンに必要とされる実際の時間の差はわずかであり得る。

[0077]

一実施形態において、基板201、102は、段階的画像キャプチャ方法によりスキャンされる。例えば、カメラはサブ画素間の既知の距離を移動する、又は画像キャプチャ間のマイクロLEDデバイスの既知の接合部位間の既知の距離を移動する。かかる実施形態において、カメラはラインスキャンカメラであってよい。一実施形態において、カメラはモザイク又は選択されたタイルをキャプチャするために画素の×・yアレイを含んだカメラであってよい。カメラの段階的画像キャプチャ動作により、基板表面の特定の領域の柔軟性を検査することが可能となり、それは離れて測定されたマイクロLEDデバイスと名目上のパターンとを比較するのに特に適し得る。したがって、カメラは一列にスキャンするよりむしろ特定の位置をキャプチャするためのパターンで移動し得る。

[0078]

数多くの可能な処理の変形例は、図8A~図8Bに関連して記述される統合検出検査の結果に基づき得る。具体的に、いくつかの実施形態において、パッシベーション層148及び上部電極層118のパターン化は、特にインクジェット印刷により堆積する場合、特定の結果に即し得る。

[0079]

図9は、本発明の一実施形態に係る、マイクロLEDデバイス400Xの欠陥又は汚損を検出後に形成され得る例示的な構造の側断面視の図である。例示の実施形態において、マイクロLEDデバイス400は検出検査において能力がある(例えば、適切な発光)であることがわかり、マイクロLEDデバイス400Xは欠陥があることがわかった。代替的に、又は追加的に、検出検査は、マイクロLEDデバイス400Xが汚損されている(例えば、上面の粒子が上部電極層との接触を妨げ得る)ことを示した。欠陥検出検査は必ずしも欠陥が何であるかを判定するものではなく、例示の実施形態においては、上部電極層118が欠陥のある又は汚損されたマイクロLEDデバイス400Xと電気的に接触することを不可能とするために、十分にマイクロLEDデバイス400Xをパッシベートするためのパッシベーション層148が、単にマイクロLEDデバイス400Xの上部に形成され得る。

[0080]

図10は、本発明の一実施形態に係る、欠落したマイクロLEDデバイスを検出後に形成され得る例示的な構造の側断面視の図である。例示の実施形態において、検出検査は、マイクロLEDデバイスが転写されていないことを示した。その結果、パッシベーション層118は上部電極層118が下部電極142と電気的に接触するのを不可能とするために、接合層140の上部に形成される。

[0081]

図11は、本発明の一実施形態に係る、欠陥のある又は汚損されたマイクロLEDデバイス400を検出後に形成され得る例示的な構造の側断面視の図である。例示するように、パッシベーション層148を形成するのに先立ち、代替のマイクロLEDデバイス400は、下部電極142上の前に開放された修復接合部位401に接合され得る。上述のように、修復接合部位401は、下部電極層142上の露出面であってよく、又は代替的に、接合層140を含み得る。代替のマイクロLEDデバイス400の配置に続き、パッシ

ベーション層148は、図9に関連して上述したように、マイクロLEDデバイス400の量子井戸構造、下部電極142、及び任意的に、欠陥のある又は汚損されたマイクロLEDデバイス400×の露出面をパッシベートするために形成されてもよい。そして上部電極118は、マイクロLEDデバイス400及び代替のマイクロLEDデバイス400と電気的に接触するように形成され得る。

#### [0082]

図12は、本発明の一実施形態に係る、マイクロLEDデバイス欠落を検出後に形成され得る例示的な構造の側断面視の図である。例示のように、パッシベーション層148を形成するのに先立ち、代替のマイクロLEDデバイス400は、下部電極142上の前に開放された修復接合部位401に接合され得る。代替のマイクロLEDデバイス400の配置に続き、パッシベーション層148は、上部電極層118が下部電極142と電気的に接触するのを不可能とするために、接合層140の上部に形成され得る。そして上部電極118は、マイクロLEDデバイス400と電気的に接触するように形成され得る。

### [0083]

図13は、本発明の実施形態に係る、図9~図12に記述される様々な構成を含むマイクロLEDデバイスのアレイの上面視の概略図である。図13に例示の特定の実施形態において、上部電極層118は、複数のバンク開口128の上部に形成され、複数のサブ画素又は画素106の上部に形成されてもよい。一実施形態において、上部電極層118は、画素エリア内のすべてのマイクロLEDデバイス400の上部に形成される。

#### [0084]

図9に例示の実施形態はまた、図13の青色発光サブ画素の1つとして示され、上部電極層118は、青色発光マイクロLEDデバイス400、及び欠陥のある又は汚損されたマイクロLEDデバイス400Xの両方の上部に形成され、欠陥のある又は汚損されたマイクロLEDデバイス400Xはパッシベーション層148で覆われている。

### [0085]

図10に例示の実施形態はまた、図13の赤色発光サブ画素の1つとして示され、上部電極層118は、赤色発光マイクロLEDデバイス400及び接合層140の両方の上部に形成され、接合層140はパッシベーション層148で覆われている。

## [0086]

図11に例示の実施形態もまた、代替の赤色発光マイクロLEDデバイス400が前に解放された修復接合部位401に接合された、図13の赤色発光サブ画素のうちの1つとして例示される。上述のように、開放された修復接合部位401は、下部電極層142上の露出面であったかもしれず、又は代替的に、接合層140を含んだかもしれない。図9と同様に、上部電極層118は、赤色発光マイクロLEDデバイス400及び欠陥のある又は汚損されたマイクロLEDデバイス400×の両方の上部に形成され、欠陥のある又は汚損されたマイクロLEDデバイス400×はパッシベーション層148で覆われている。

### [0087]

図12に例示の実施形態もまた、代替の青色発光マイクロLEDデバイス400が前に解放された修復接合部位401に接合された、図13の青色発光サブ画素のうちの1つとして例示される。図10と同様に、上部電極層118は、青色発光マイクロLEDデバイス400及び接合層140の両方の上部に形成され、接合層140はパッシベーション層148で覆われている。

## [ 0 0 8 8 ]

図14は、本発明の実施形態に係る、図9~図12に記述される様々な構成を含むマイクロLEDデバイスのアレイの上面視の概略図である。図13に例示の特定の実施形態において、マイクロLEDデバイス400の配置は、図13に例示のものとは、特に複数の別個の上部電極層118の形成において、異なる。一実施形態において、マイクロLEDデバイ

10

20

30

40

ス400が修復接合部位401上に配置されない、ラベル付きの画素106内に例示のものように、上部電極層118は、その上に形成されることが要求されない。したがって、上部電極層118の長さは、代替のマイクロLEDデバイスが追加されるかどうかに基づいて決定され得る。加えて、ラベル付き画素106内の青色発光サブ画素は、接地タイラインから更に離れた接合部位上の欠陥のある又は汚損されたマイクロLEDデバイス400×を示す。かかる実施形態において、上部電極層118は、青色発光マイクロLEDデバイス400及び欠陥のある若しくは汚損されたマイクロLEDデバイス400及び欠陥のある若しくは汚損されたマイクロLEDデバイス400×の両方の上部に形成されてもよい。上部電極層118はまた、接合部位401の上部に形成されてもよい。【0089】

10

20

30

40

図15は、本発明の実施形態に係る、図9~図12に記述される様々な構成を含むマイクロLEDデバイスのアレイの上面視の概略図である。図15に例示の特定の実施形態において、マイクロLEDデバイス400の配置は、図13~図14に関連して上述されたものと同じである。図15に例示された実施形態は、図14に例示のものとは、特に複数の別個の上部電極層118の形成において、異なる。図14に例示の実施形態は、上部で極層118の長さを変更するものとして示されたが、図15に例示の実施形態は、上部で極層118の通路及び/又は上部電極層118の数を変更するものとして示される。例えば、図15に例示の実施形態の多くにおいて、別個の上部電極層118は、マイクロLEDデバイス400年に形成されてもよい。例示の実施形態において、最下部の青色発光れた複数のLEDデバイス年がして、又は代替的に、欠陥のある若しくは汚損されたマイクロLEDデバイスに対して形成されてもよい。このように、上部で極層118の通路を調整することは、欠陥のある若しくは汚損されたマイクロLEDデバイスの接合部位を覆うためのパッシベーション層148の蒸着を調整することの代替案として又はそれに加えて、使用され得る。

[0090]

別個の上部電極層(複数も可)118の形成は、上部電極層(複数も可)118の形成後のパネル100の電気的検査の間、追加の利点を提供し得る。例えば、上部電極層118の形成に先立ち、マイクロLEDデバイス400Sの短絡を生じさせる、ある欠陥を検出することを可能ではなかったであろう。短絡したマイクロLEDデバイス400Sのでは、すべての電流がサブ画素内の他のマイクロLEDデバイスのいずれかよりもむしたマイクロLEDデバイス400Sに接続したマイクロLEDデバイス400Sに接続したマイクロLEDデバイス400Sに接続したマイクロLEDデバイス400Sに接続された上部電極層118は、レーザスクライビング等の適した技術を使用して切断される。このように、上述の統合検査方法の間に検出され得なかった又は検出されていなかった気的短絡は、潜在的に、上部電極層118の形成後の表示を通して電流を印加した電気的短絡は、潜在的に、上部電極層118の形成後の表示を通して電流を印加した電気的短絡した場合、マイクロLEDデバイス400Sに対する上部電極層118は切断でき、それにより冗長性及び/又は修復マイクロLEDデバイスがサブ画素からの発光を提供できるようになる。

[0091]

図17は、上部電極層118を切断又はスクライブするよりむしろ、不規則なマイクロLEDデバイスを分離するために、下部電極層142がレーザスクライビング等の適した技術を使用して切断され得る。例示の特定の実施形態において、下部電極層124は、マイクロLEDデバイスの別個のランディングエリアを含む。例示の特定の実施形態において、マイクロLEDデバイス400Sを支持する下部電極124のランディングエリアは、充填された開口131を通して基本TFT回路と電気的通信状態にさせないように、不規則なマイクロLEDデバイスを分離するために、レーザスクライビング等の適切な技術を使用して切断される。

[0092]

20

30

図18は、一実施形態に係るディスプレイシステム1800を示す。ディスプレイシステムは、プロセッサ1810、データ受信機1820、上述のディスプレイパネルのいずれかのようなディスプレイパネル100、200を収容する。データ受信機1820は、無線又は有線でデータを受信するように構成され得る。無線はWi-Fi(登録商標)(IEEE802.16、ファミリー)、IEEE802.16、ファミリー)、IEEE802.20、ロングタームエボルーション(LTE)、Ev-Do、HSPA+、HSDPA+、HSUPA+、EDGE、GSM(登録商標)、GPRS、CDMA、TDMA、DECT、Bluetooth(登録商標)、それらの誘導体、並びに3G、4G、5G、及びそれを越えるものとして設計された他のいかなる無線プロトコルを含むが、それに限定されない、多数の無線規格又はプロトコルのいずれかにおいて実施され得る。

[0093]

その用途により、ディスプレイシステム 1 8 0 0 は他のコンポーネンツを含んでもよい。これらの他のコンポーネンツは、メモリ、タッチスクリーンコントローラ、及びバッテリを含むが、それらに限定されない。様々な実装において、ディスプレイシステム 1 8 0 0 は、テレビ、タブレット、電話、ラップトップ、コンピュータモニタ、キオスク、デジタルカメラ、ハンドヘルドゲームコンソール、メディアディスプレイ、電子ブックディスプレイ、又は広域サイネージディスプレイであってよい。

[0094]

本発明の様々な側面の利用において、上記実施形態の組み合わせ又は変更が冗長性システム及び修復部位をアクティブマトリクス型ディスプレイパネルに統合、並びに欠落した、欠陥のある、又は汚損されたマイクロLEDデバイス等のマイクロLEDデバイスのアレイにおける不規則部分を検出するための検査方法を統合することが可能であることは、当業者にとって明らかであろう。

[0095]

上記実施形態はアクティブマトリクス型ディスプレイパネルに関連して記述されてきたが、冗長性スキーム、修復部位、及び欠落した、欠陥のある、又は汚損されたマイクロレビスを検出するための検査方法はまた、照明の目的のための基板並びにパッシェン構造に関連して記述されてきたが、本発明の実施形態はトップエミッション構造に関連して記述されてきたが、本発明の実施形態はまた、ボトムゲートトラジスタ構造が記述されてきたが、本発明の実施形態はまた、ボトムゲートトラジスタ構造においても実施できる。更に、米明の実施形態は、ハイサイド駆動構成に関連して記述及び例示されてきたが、本発明の実施形態は、ハイサイド駆動構成に関連して記述及び例示されてきたが、本発はまた、上述の接地タイライン及び接地リングがパネルにおいて電カラインとなるローサイド駆動構成でも実施できる。本発明は、構造上の特徴及び/又は方法論的行為に特有ので記述されてきたが、添付の請求項で規定される本発明は、必ずしも記述される特定の特徴又は行為に限定されないことを理解すべきである。むしろ、記載の特定の特徴及び行為は、本発明を例示する上で有用な、請求の発明の特に上手な実施であるとして理解されるべきである。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

## 【図4F】

# 【図4G】

【図4H】

## 【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図6A】

【図6B】

【図 6 C】

【図6D】

【図7】

【図8A】

【図8B】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

### フロントページの続き

(72)発明者 ビブル アンドレアス

アメリカ合衆国 カリフォルニア州 95054 サンタ クララ ワイヤット ドライブ 17

(72)発明者 サカリヤ カピル ヴィ

アメリカ合衆国 カリフォルニア州 95054 サンタ クララ ワイヤット ドライブ 17

(72)発明者 グリッグス チャールズ アール

アメリカ合衆国 カリフォルニア州 95054 サンタ クララ ワイヤット ドライブ 17

(72)発明者 パーキンス ジェイムズ マイケル

アメリカ合衆国 カリフォルニア州 95054 サンタ クララ ワイヤット ドライブ 17

0 5

## 審査官 村川 雄一

(56)参考文献 特開2005-085737(JP,A)

特開2012-227514(JP,A)

特開2012-089572(JP,A)

特表2005-509290(JP,A)

特開2008-065200(JP,A)

特開2000-195677(JP,A)

特開2009-122652(JP,A)

国際公開第2003/041157(WO,A1)

米国特許出願公開第2012/0256814(US,A1)

米国特許出願公開第2012/0092389(US,A1)

米国特許出願公開第2008/0062096(US,A1)

米国特許出願公開第2009/0102753(US,A1)

米国特許第06514779(US, B1)

欧州特許出願公開第01444729(EP,A1)

中国特許出願公開第102737578(CN,A)

中国特許出願公開第1605124(CN,A)

中国特許出願公開第101202014(CN,A)

台湾特許出願公開第201303832(TW,A)

韓国公開特許第10-2004-0052234(KR,A)

## (58)調査した分野(Int.CI., DB名)

G 0 9 F 9/33

G 0 9 F 9/302

H01L 33/00

| 专利名称(译)        | 具有冗余方案的发光二极管显示面标                                                                                      | 反       |            |  |

|----------------|-------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | JP6254674B2                                                                                           | 公开(公告)日 | 2017-12-27 |  |

| 申请号            | JP2016500743                                                                                          | 申请日     | 2014-03-06 |  |

| [标]申请(专利权)人(译) | 力士视图技术公司                                                                                              |         |            |  |

| 申请(专利权)人(译)    | 力士视图技术公司                                                                                              |         |            |  |

| 当前申请(专利权)人(译)  | 苹果公司                                                                                                  |         |            |  |

| [标]发明人         | ビブルアンドレアス<br>サカリヤカピルヴイ<br>グリッグスチャールズアール<br>パーキンスジェイムズマイケル                                             |         |            |  |

| 发明人            | ビブル アンドレアス<br>サカリヤ カピル ヴイ<br>グリッグス チャールズ アール<br>パーキンス ジェイムズ マイケル                                      |         |            |  |

| IPC分类号         | G09F9/33 G09F9/302 H01L33/00                                                                          |         |            |  |

| CPC分类号         | H01L25/0753 H01L24/95 H01L27/1214 H01L27/1259 H01L33/0095 H01L2924/0002 H01L2924/12041 H01L2924/12044 |         |            |  |

| FI分类号          | G09F9/33 G09F9/302.C H01L33/00.L                                                                      |         |            |  |

| 代理人(译)         | 田中真一郎西岛隆义                                                                                             |         |            |  |

| 优先权            | 13/842879 2013-03-15 US<br>13/842925 2013-03-15 US                                                    |         |            |  |

| 其他公开文献         | JP2016512347A                                                                                         |         |            |  |

| 外部链接           | <u>Espacenet</u>                                                                                      |         |            |  |

## 摘要(译)

描述了显示面板和制造方法。在一个实施例中,显示基板包括像素区域和非像素区域。子像素阵列和相应下电极阵列位于像素区域中。微LED器件阵列与下电极阵列结合。形成一个或多个上电极层,与微LED器件阵列电接触。在一个实施例中,冗余的微LED器件对结合到下电极阵列。在一个实施例中,对微LED器件阵列进行成像以检测不规则性。

| (19) <b>日本国特許庁(JP)</b> | (12) 特                    | 許 公 幸        | <b>报 (B2)</b> (11) 特許番号                                |

|------------------------|---------------------------|--------------|--------------------------------------------------------|

|                        |                           |              | 特許第6254674号                                            |

| (45) 発行日 平成 <b>29年</b> | 12月27日 (2017.12.27)       |              | ( <b>P6254674</b> )<br>(24) 登録日 平成29年12月8日 (2017.12.8) |

| (51) Int.Cl.           | FI                        |              |                                                        |

| GO9F 9/33              | (2006.01) GC              | 9 F 9/33     |                                                        |

| GO9F 9/302             | (2006.01) GC              | 9 F 9/302    | C                                                      |

| HO1L 33/00             | (2010.01) H C             | 0 1 L 33/00  | L                                                      |

|                        |                           |              |                                                        |

|                        |                           |              | 請求項の数 17 (全 35 頁)                                      |

| (21) 出願番号 1            | 寺願2016-500743 (P2016-500) | 743) (73) 特許 | 権者 503260918                                           |

| (86) (22) 出願日 3        | 平成26年3月6日 (2014.3.6)      |              | アップル インコーポレイテッド                                        |

| (65) 公表番号 年            | 特表2016-512347 (P2016-512) | 347A)        | アメリカ合衆国 95014 カリフォル                                    |

| (43) 公表日 3             | 平成28年4月25日 (2016.4.25)    | ·            | ニア州 クパチーノ インフィニット ル                                    |

| (86) 国際出願番号 F          | PCT/US2014/021259         |              | ープ 1                                                   |

| (87) 国際公開番号 ¥          | 02014/149864              | (74) 代理      | 人 100094569                                            |

| (87) 国際公開日 3           | 平成26年9月25日 (2014. 9. 25)  | · II         | 弁理士 田中 伸一郎                                             |

| 審査請求日 3                | 平成27年11月13日 (2015.11.1    | 13) (74)代理   | 人 100088694                                            |

|                        | 3/842, 879                |              | 弁理士 弟子丸 健                                              |

|                        | 平成25年3月15日 (2013.3.15)    | (74)代理       | 人 100067013                                            |

| (33) 優先権主張国 >          | 株国 (US)                   |              | 弁理士 大塚 文昭                                              |

| (31) 優先権主張番号 1         | 3/842, 925                | (74) 代理      | 人 100086771                                            |

| (32) 優先日 3             | 平成25年3月15日 (2013.3.15)    | ·            | 弁理士 西島 孝喜                                              |

| (33) 優先権主張国            | 米国 (US)                   |              |                                                        |

| 前置審査                   |                           |              | 最終百に続く                                                 |